基于FPGA的多通道校准算法同步实现

时间:07-20

来源:互联网

点击:

源直接构建,不仅难以保证理想的运算速度,而且硬件开销非常巨大。而FPGA芯片内部已经集成了18×18位的硬件乘法器模块,其速度快,实现简单,能有效节省FPGA的逻辑资源。由于系统设计时选用的FPGA芯片型号为Xilinx公司的xc2v8000ff1152-5,它集成了几百个硬件乘法器,因此可以全部使用硬件乘法器来完成相应的乘法运算。

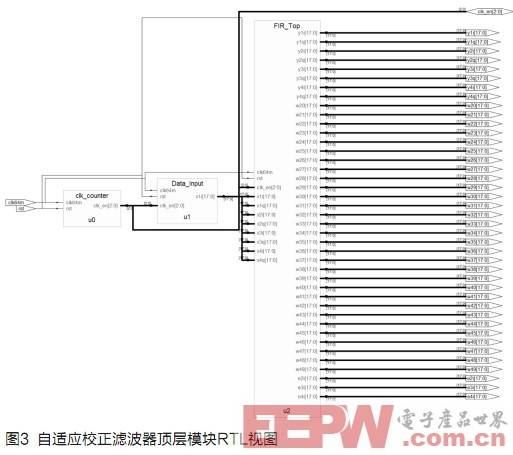

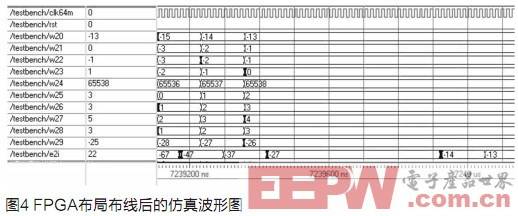

采用VHDL语言编写实现程序,开发环境为ISE 8.2i,综合工具为Synplify Pro v8.1,仿真工具为ModelSim SE 6.3f。图3所示的是程序经Synplify Pro v8.1综合后得到的LMS自适应校正滤波器顶层模块RTL视图。RTL视图即寄存器传输级视图,该图高度抽象为模块化结构,它是在对源代码编译后再现设计的寄存器传输级原理图。

表1为多通道校准算法的FPGA资源占用列表,从系统资源占用情况可以看出:多通道校准算法FPGA实现过程中,如果再加上前后端处理程序一起编译,则输入输出端口将减少,资源占用也将减少,并不影响系统实现。其它各种资源占用量都较少,完全符合FPGA设计要求。

由于数据时钟的同步是FPGA 芯片设计实现的一个常见问题,也是一个重点和难点,很多设计不稳定都是源于数据时钟的同步有问题。而本文提出了解决这一问题的时钟同步方法,并在硬件上很好地实现了多通道校准算法,极大提高了系统稳定性。

采用VHDL语言编写实现程序,开发环境为ISE 8.2i,综合工具为Synplify Pro v8.1,仿真工具为ModelSim SE 6.3f。图3所示的是程序经Synplify Pro v8.1综合后得到的LMS自适应校正滤波器顶层模块RTL视图。RTL视图即寄存器传输级视图,该图高度抽象为模块化结构,它是在对源代码编译后再现设计的寄存器传输级原理图。

表1为多通道校准算法的FPGA资源占用列表,从系统资源占用情况可以看出:多通道校准算法FPGA实现过程中,如果再加上前后端处理程序一起编译,则输入输出端口将减少,资源占用也将减少,并不影响系统实现。其它各种资源占用量都较少,完全符合FPGA设计要求。

由于数据时钟的同步是FPGA 芯片设计实现的一个常见问题,也是一个重点和难点,很多设计不稳定都是源于数据时钟的同步有问题。而本文提出了解决这一问题的时钟同步方法,并在硬件上很好地实现了多通道校准算法,极大提高了系统稳定性。

ADC 无线电 DSP Xilinx FPGA 电路 滤波器 VHDL 仿真 ModelSim 相关文章:

- 新一代移动通信系统的关键技术(10-26)

- SoC面临挑战,智能分割顺势而起(11-07)

- 宽带通信接收机的ADC参数(01-12)

- Broadcom升级定位服务网络 添加Wi-Fi定位(09-30)

- Broadcom公司新型安全应用处理器系列掌握防止数据盗窃和身份假冒的关键(11-19)

- ADC 59M1室外型分光配线箱解决方案(01-16)