EMI/EMC设计讲座(四)印刷电路板的映像平面

时间:07-20

来源:互联网

点击:

接地和讯号回路

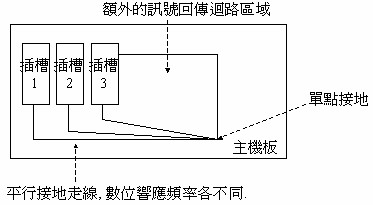

由于回路是射频能量传播最主要的媒介,因此,接地或讯号回传回路控制(return loop control)是抑制PCB内的电磁干扰的最重要设计考虑之一。高速的逻辑组件和振荡器应该尽量靠近接地电路,以避免形成回路;在此回路中会有涡流(eddy current)存在,此时是以机壳或底座(chassis)接地。涡流是受到不断变化的磁场感应产生的,它通常是寄生的。附图五是PC的适配卡插槽和单点接地所形成的回路。在此图中,有一个额外的讯号回传回路区域存在。每个回路将会各别产生一个不同的电磁场和频谱。射频电流将会在特定的频率下,产生电磁辐射场,其辐射能量的大小和回路的面积有关。这时必须使用遮蔽物(containment),以避免射频电流耦合至其它电路中;或辐射至外部环境,造成电磁干扰。不过,最好能尽量避免由内部电路产生射频回路电流(RF loop current)来。

若射频电流的回传路径不存在,此时,可以利用连接至底座的接地线路,或0V参考源来协助移

除掉不良的射频电流。这也称为「回路面积控制(loop area control)」。

回路面积的控制

一个被磁场感应的回路,它的电磁场可以用电压源来表示。这个电压源大小和回路的总面积成正比。因此,为了降低磁场的耦合效应,必须减少回路的面积。电场「捡拾(pickup)」接收系统也是依靠回路面积,来形成接收天线。

当有一个电场存在时,在电源和接地平面之间,会产生一个电流源。电场不会在线路至线路之间耦合,而会在走线至接地线之间耦合,这就包含了共模电流。但是,对磁场而言,由于电场会伴随它产生,所以电磁场会在线路至线路之间耦合,也会在走线至接地线之间耦合。

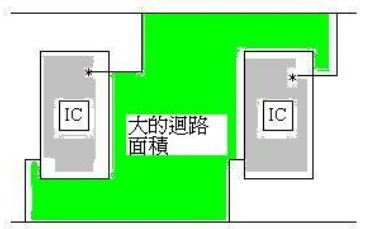

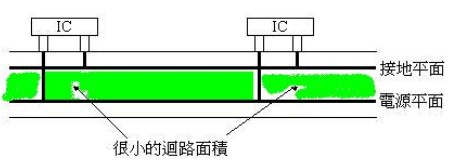

一般人都会忽略在PCB内,于电源和0V参考点之间要设置回路区域。附图六的大回路面积是最容易设计的,但也最容易被「静电释放(ESD)」或其它场感应,变成一个天线。多层堆栈的PCB可以减轻ESD的破坏,并能减少磁场的产生,避免它辐射至自由空间。在附图七中,接地平面和电源平面之间,具有一个很小的回路面积。

使用电源和接地平面可以降低电源分配系统的电感值。若将电源分配系统的特性阻抗降低,则可以降低电路板的电压降。电压降若变小,则「接地弹跳(ground bounce)」的现象就可以避免。当逻辑闸开关快速切换时,瞬间的电流变化会经由IC接脚,传送至主机板的电源平面或接地平面,造成输入参考电压的波动,进而产生射频噪声(RF noise)和电磁干扰,这种现象就称作「接地弹跳(ground bounce)」。此外,降低特性阻抗的同时,电源平面与接地平面之间的电容值会增加,这个电容值会使得任何的感应电压值下降,这就是「去耦合(decouple)」的效果。

当讯号线在组件之间穿梭时,大的回路面积就被产生了。但是我们常常会忘记讯号线对EMI的影响。虽然,讯号的完整性(时域)仍然很高,但是,EMI依然存在(频域),因为讯号回路面积所产生的问题,比电源分配系统所产生的问题多。尤其是从ESD的观点来分析,更是如此;这是由于ESD会直接进入回路和组件的输入脚位中。为了降低ESD可能造成的伤害,减少回路面积是最简单的方法。电源和接地平面分散网络提供了低阻抗的路径,能够将ESD能量传送至0V的回传参考平面内。毕竟,回路是回路,如果它们能发出电磁波,就应该能够接收电磁波。

除了能降低接地噪声电压以外,映像平面也能防止射频接地回路变大,因为射频电流紧密地与它们的电流源走线耦合,所以,它不需要另外寻找回传路径。当回路控制最大化时,磁通量就被大幅消除了。这是在PCB内,抑制射频电流的最重要观念之一。在靠近每一个讯号平面处,正确地配置映像平面,就可以消除共模的射频电流。传输大量的射频电流的映像平面,必须接地或接至0V参考点。为了移除多余的射频电压和涡流,所有接地和底座平面可以透过一个低阻抗的接地电路,连接至底座的接地点。

要降低PCB内的回路生成,最简单的方法是设计许多个接地线,并全部连接至底座的接地点。由于组件的输出讯号的边缘速率(edge rate)加快了,所以,多点接地就变成了必要的规格,尤其当有使用到I/O互连的设计时。当PCB使用多点接地,而且都连接到一个金属结构上,这时,我们必须知道所有接地线之间的间距是多少。

接地线之间的距离不能超过最高频率的λ/20,这不仅包括主频率,也包含谐波频率。如果某组件的输出讯号的边缘速率比较慢,则它连接至底座接地点的数目可以减少,或和接地位置的距离可以增加。例如:一个64MHz的振荡器的λ/20是23.4公分,若两个接地线的直线距离大于23.4公分,则很可能会有射频回路存在,这个回路可能就是射频能量传播的来源。

在PCB中的组件布局必须要正确。将不同功能区块的接地线紧密相邻,可以缩短讯号走线的长度、降低反射、并使绕线容易,同时保持讯号的完整性。应该要尽量避免使用通孔(via),因为每一个通孔会增加走线的电感值大约1至3 nH。

此外,为了防止不同的频宽区域相互耦合,必须对不同的功能区块做正确的分割(partition),其方法有:使用分离的PCB、绝缘、不同的布线….等。正确的分割可以提高电路效能、使绕线容易、缩短走线的长度,并且能缩小回路的面积、提升讯号质量。工程师在布线之前,必须先规划好哪些组件是属于哪一个功能区块,而这些信息可以从组件供货商处获得。

由于回路是射频能量传播最主要的媒介,因此,接地或讯号回传回路控制(return loop control)是抑制PCB内的电磁干扰的最重要设计考虑之一。高速的逻辑组件和振荡器应该尽量靠近接地电路,以避免形成回路;在此回路中会有涡流(eddy current)存在,此时是以机壳或底座(chassis)接地。涡流是受到不断变化的磁场感应产生的,它通常是寄生的。附图五是PC的适配卡插槽和单点接地所形成的回路。在此图中,有一个额外的讯号回传回路区域存在。每个回路将会各别产生一个不同的电磁场和频谱。射频电流将会在特定的频率下,产生电磁辐射场,其辐射能量的大小和回路的面积有关。这时必须使用遮蔽物(containment),以避免射频电流耦合至其它电路中;或辐射至外部环境,造成电磁干扰。不过,最好能尽量避免由内部电路产生射频回路电流(RF loop current)来。

图五:在PCB内的接地回路

若射频电流的回传路径不存在,此时,可以利用连接至底座的接地线路,或0V参考源来协助移

除掉不良的射频电流。这也称为「回路面积控制(loop area control)」。

回路面积的控制

一个被磁场感应的回路,它的电磁场可以用电压源来表示。这个电压源大小和回路的总面积成正比。因此,为了降低磁场的耦合效应,必须减少回路的面积。电场「捡拾(pickup)」接收系统也是依靠回路面积,来形成接收天线。

当有一个电场存在时,在电源和接地平面之间,会产生一个电流源。电场不会在线路至线路之间耦合,而会在走线至接地线之间耦合,这就包含了共模电流。但是,对磁场而言,由于电场会伴随它产生,所以电磁场会在线路至线路之间耦合,也会在走线至接地线之间耦合。

一般人都会忽略在PCB内,于电源和0V参考点之间要设置回路区域。附图六的大回路面积是最容易设计的,但也最容易被「静电释放(ESD)」或其它场感应,变成一个天线。多层堆栈的PCB可以减轻ESD的破坏,并能减少磁场的产生,避免它辐射至自由空间。在附图七中,接地平面和电源平面之间,具有一个很小的回路面积。

使用电源和接地平面可以降低电源分配系统的电感值。若将电源分配系统的特性阻抗降低,则可以降低电路板的电压降。电压降若变小,则「接地弹跳(ground bounce)」的现象就可以避免。当逻辑闸开关快速切换时,瞬间的电流变化会经由IC接脚,传送至主机板的电源平面或接地平面,造成输入参考电压的波动,进而产生射频噪声(RF noise)和电磁干扰,这种现象就称作「接地弹跳(ground bounce)」。此外,降低特性阻抗的同时,电源平面与接地平面之间的电容值会增加,这个电容值会使得任何的感应电压值下降,这就是「去耦合(decouple)」的效果。

图六:绿色区域是大的回路面积

当讯号线在组件之间穿梭时,大的回路面积就被产生了。但是我们常常会忘记讯号线对EMI的影响。虽然,讯号的完整性(时域)仍然很高,但是,EMI依然存在(频域),因为讯号回路面积所产生的问题,比电源分配系统所产生的问题多。尤其是从ESD的观点来分析,更是如此;这是由于ESD会直接进入回路和组件的输入脚位中。为了降低ESD可能造成的伤害,减少回路面积是最简单的方法。电源和接地平面分散网络提供了低阻抗的路径,能够将ESD能量传送至0V的回传参考平面内。毕竟,回路是回路,如果它们能发出电磁波,就应该能够接收电磁波。

除了能降低接地噪声电压以外,映像平面也能防止射频接地回路变大,因为射频电流紧密地与它们的电流源走线耦合,所以,它不需要另外寻找回传路径。当回路控制最大化时,磁通量就被大幅消除了。这是在PCB内,抑制射频电流的最重要观念之一。在靠近每一个讯号平面处,正确地配置映像平面,就可以消除共模的射频电流。传输大量的射频电流的映像平面,必须接地或接至0V参考点。为了移除多余的射频电压和涡流,所有接地和底座平面可以透过一个低阻抗的接地电路,连接至底座的接地点。

图七:具有一个很小的回路面积的PCB布线

接地线的间距

要降低PCB内的回路生成,最简单的方法是设计许多个接地线,并全部连接至底座的接地点。由于组件的输出讯号的边缘速率(edge rate)加快了,所以,多点接地就变成了必要的规格,尤其当有使用到I/O互连的设计时。当PCB使用多点接地,而且都连接到一个金属结构上,这时,我们必须知道所有接地线之间的间距是多少。

接地线之间的距离不能超过最高频率的λ/20,这不仅包括主频率,也包含谐波频率。如果某组件的输出讯号的边缘速率比较慢,则它连接至底座接地点的数目可以减少,或和接地位置的距离可以增加。例如:一个64MHz的振荡器的λ/20是23.4公分,若两个接地线的直线距离大于23.4公分,则很可能会有射频回路存在,这个回路可能就是射频能量传播的来源。

在PCB中的组件布局必须要正确。将不同功能区块的接地线紧密相邻,可以缩短讯号走线的长度、降低反射、并使绕线容易,同时保持讯号的完整性。应该要尽量避免使用通孔(via),因为每一个通孔会增加走线的电感值大约1至3 nH。

此外,为了防止不同的频宽区域相互耦合,必须对不同的功能区块做正确的分割(partition),其方法有:使用分离的PCB、绝缘、不同的布线….等。正确的分割可以提高电路效能、使绕线容易、缩短走线的长度,并且能缩小回路的面积、提升讯号质量。工程师在布线之前,必须先规划好哪些组件是属于哪一个功能区块,而这些信息可以从组件供货商处获得。

电路 PCB 电压 射频 电流 电容 电感 EMC 电阻 CMOS 振荡器 相关文章:

- 点评:全方位剖析中国集成电路核心技术发展之困(01-08)

- 布线工程师如何充分掌控时钟信号?(02-01)

- 高速数字电路设计之串音分析(11-01)

- PCB反设计系统中的探测电路(02-18)

- PCB电路版图设计的常见问题 (11-01)

- 电源完整性分析应对高端PCB系统设计挑战(11-01)