基于电磁兼容的PCB设计

时间:08-13

来源:互联网

点击:

PCB是英文(Printed Circuit Board)印制线路板的简称。通常把在绝缘材料上,按预定设计,制成印制线路、印制元件或两者组合而成的导电图形称为印制电路。而在绝缘基材上提供元器件之间电气连接的导电图形,称为印制线路。这样就把印制电路或印制线路的成品板称为印制线路板,亦称为印制板或印制电路板。PCB几乎我们所能见到的电子设备都离不开它,小到电子手表、计算器、通用电脑,大到计算机、通讯电子设备、航空、航天、军用武器系统,只要有集成电路等电子元器件,它们之间电气互连都要用到PCB,它的性能直接关系到电子设备质量的好坏。随着电子技术的飞速发展,电子产品越来越趋向高速,高灵敏度,高密度,这种趋势导致了PCB电路板设计中的电磁兼容(EMC)和电磁干扰问题严重化,电磁兼容设计已成为PCB设计中急待解决的技术难题。

1 电磁兼容

电磁兼容(Electro—Magnetic Compatibility,简称EMC)是一门新兴综合性学科,它主要研究电磁干扰和抗干扰问题。电磁兼容性是指电子设备或系统在规定的电磁环境电平下,不因电磁干扰而降低性能指标,同时它们本身产生的电磁辐射不大于限定的极限电平,不影响其它系统的正常运行,并达到设备与设备、系统与系统之间互不干扰、共同可靠工作的目的。电磁干扰(EMI)产生是由于电磁干扰源通过耦合路径将能量传递给敏感系统造成的,它包括由导线和公共地线的传导、通过空间辐射或近场耦合3种基本形式。实践证明,即使电路原理图设计正确,印制电路板设计不当,也会对电子设备的可靠性产生不利影响,所以保证印制电路板电磁兼容性是整个系统设计的关键。

1.1 电磁干扰(EMI)

当一个EMI问题产生时,需要用3个元素来描述:干扰源、传播路径和接受者。如图1所示:

因此我们要减小电磁干扰,就要在这三个元素上去想办法。下面我们主要讨论印制电路板的布线技术。

2 印制电路板的布线技术

良好的印制电路板(PCB)布线在电磁兼容性中是一个非常重要的因素。

2.1 PCB基本特性

一个PCB的构成是在垂直叠层上使用了一系列的层压、走线和预浸处理。在多层PCB中,设计者为了方便调试,会把信号线布在最外层。

PCB上的布线是有阻抗、电容和电感特性的。

阻抗:布线的阻抗是由铜和横切面面积的重量决定的。例如,l盎司铜则有O.49 mΩ/单位面积的阻抗。电容:布线的电容是由绝缘体(EoEr)、电流到达的范围(A)以及走线间距(h)决定的。用等式表达为C=EoErA/h,Eo是自由空间的介电常数(8.854 pF/m),Er是PCB基体的相关介电常数(在FR4碾压中为4.7)。

电感:布线的电感平均分布在布线中,大约为1 nH/m。

对于1盎司铜线来说,在O.25 mm(10mil)厚的FR4碾压情况下,位于地线层上方的0.5 mm(20 mil)宽,20 mm(800 mil)长的线能产生9.8 m∧的阻抗,20 nH的电感以及与地之间1.66 pF的耦合电容。将上述值与元器件的寄生效应相比,这些都是可以忽略不计的,但所有布线的总和可能会超出寄生效应。因此,设计者必须将这一点考虑进去。PCB布线的普遍方针:

(1)增大走线的间距以减少电容耦合的串扰;

(2)平行的布电源线和地线以使PCB电容达到最佳;

(3)将敏感的高频线布在远离高噪声电源线的地方;

(4)加宽电源线和地线以减少电源线和地线的阻抗。

2.2 分割

分割是指用物理上的分割来减少不同类型线之间的耦合,尤其是通过电源线和地线。

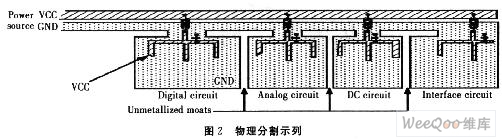

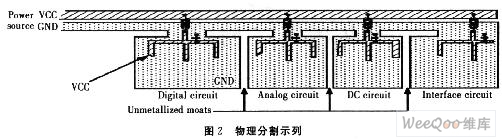

图2给出了用分割技术将4个不同类型的电路分割开的例子。在地线面,非金属的沟用来隔离四个地线面。L和C作为板子上的每一部分的过滤器.减少不同电路电源面间的耦合。高速数字电路由于其更高的瞬时功率需量而要求放在电源入口处。接口电路可能会需要静电释放(ESD)和暂态抑制的器件或电路。对于L和C来说,最好使用不同值的L和C,而不是用一个大的L和C,因为这样它便可以为不同的电路提供不同的滤波特性。

2.3 局部电源和IC间的去耦

局部去耦能够减少沿着电源干线的噪声传播。连接着电源输入口与PCB之间的大容量旁路电容起着一个低频脉动滤波器的作用,同时作为一个电势贮存器以满足突发的功率需求。此外,在每个IC的电源和地之间都应当有去耦电容.这些去耦电容应该尽可能的接近引脚。这将有助于滤除IC的开关噪声。

2.4 接地技术

接地技术既应用于多层PCB,也应用于单层PCB。接地技术的目标是最小化接地阻抗,以此减少从电路返回到电源之间的接地回路的电势。

(1)单层PCB的接地线

在单层(单面)PCB中,接地线的宽度应尽可能的宽,且至少应为1.5 mm(60 mil)。由于在单层PCB上无法实现星形布线,因此跳线和地线宽度的改变应当保持为最低,否则将引起线路阻抗与电感的变化。

(2)双层PCB的接地线

在双层(双面)PCB中,对于数字电路优先使用地格栅/点阵布线,这种布线方式可以减少接地阻抗,接地回路和信号环路。像在单层PCB中,地线和电源线的宽度最少应为1.5 mm。另外的一种布局是将接地层放在一边,信号和电源线放于另一边。在这种布置方式中将进一步减少接地回路和阻抗,去耦电容可以放置在距离IC供电线和接地层之间尽可能近的地方。

(3)保护环

保护环是一种可以将充满噪声的环境(比如射频电流)隔离在环外的接地技术,这是因为在通常的操作中没有电流流过保护环。

(4)PCB电容

在多层板上,由分离电源面和地面的绝缘薄层产生了PCB电容。在单层板上,电源线和地线的平行布放也将导致这种电容效应。PCB电容的一个优点是它具有非常高的频率响应和均匀的分布在整个面或整条线上的低串连电感。它等效于一个均匀分布在整个板上的去耦电容。没有任何一个单独的分立元件具有这个特性。

(5)高速电路与低速电路

布放高速电路时应使其更接近接地面,而低速电路应使其接近电源面。

(6)地的铜填充

在某些模拟电路中,没有用到的电路板区域是由一个大的接地面来覆盖,以此提供屏蔽和增加去耦能力。但是假如这片铜区是悬空的(比如它没有和地连接),那么它可能表现为一个天线,并将导致电磁兼容问题。

(7)多层PCB中的接地面和电源面

在多层PCB中,推荐把电源面和接地面尽可能近的放置在相邻的层中,以便在整个板上产生一个大的PCB电容。速度最快的关键信号应当临近接地面的一边,非关键信号则布放为靠近电源面。

(8)电源要求

当电路需要不止一个电源供给时,采用接地将每个电源分离开。但是在单层PCB中多点接地是不可能的。一种解决方法是把从一个电源中引出的电源线和地线同其他的电源线和地线分隔开。这同样有助于避免电源之间的噪声耦合。

3 结束语

本文所介绍的各种方法与技巧有利于提高PCB的EMC特性,当然这些只是EMC设计中的一部分,通常还要考虑反射噪声,辐射发射噪声,以及其他工艺技术问题引起的干扰。在实际的设计中,应根据设计的目标要求和设计条件,采用合理的抗电磁干扰措施,设计出具有良好EMC性能的PCB电路板。

1 电磁兼容

电磁兼容(Electro—Magnetic Compatibility,简称EMC)是一门新兴综合性学科,它主要研究电磁干扰和抗干扰问题。电磁兼容性是指电子设备或系统在规定的电磁环境电平下,不因电磁干扰而降低性能指标,同时它们本身产生的电磁辐射不大于限定的极限电平,不影响其它系统的正常运行,并达到设备与设备、系统与系统之间互不干扰、共同可靠工作的目的。电磁干扰(EMI)产生是由于电磁干扰源通过耦合路径将能量传递给敏感系统造成的,它包括由导线和公共地线的传导、通过空间辐射或近场耦合3种基本形式。实践证明,即使电路原理图设计正确,印制电路板设计不当,也会对电子设备的可靠性产生不利影响,所以保证印制电路板电磁兼容性是整个系统设计的关键。

1.1 电磁干扰(EMI)

当一个EMI问题产生时,需要用3个元素来描述:干扰源、传播路径和接受者。如图1所示:

因此我们要减小电磁干扰,就要在这三个元素上去想办法。下面我们主要讨论印制电路板的布线技术。

2 印制电路板的布线技术

良好的印制电路板(PCB)布线在电磁兼容性中是一个非常重要的因素。

2.1 PCB基本特性

一个PCB的构成是在垂直叠层上使用了一系列的层压、走线和预浸处理。在多层PCB中,设计者为了方便调试,会把信号线布在最外层。

PCB上的布线是有阻抗、电容和电感特性的。

阻抗:布线的阻抗是由铜和横切面面积的重量决定的。例如,l盎司铜则有O.49 mΩ/单位面积的阻抗。电容:布线的电容是由绝缘体(EoEr)、电流到达的范围(A)以及走线间距(h)决定的。用等式表达为C=EoErA/h,Eo是自由空间的介电常数(8.854 pF/m),Er是PCB基体的相关介电常数(在FR4碾压中为4.7)。

电感:布线的电感平均分布在布线中,大约为1 nH/m。

对于1盎司铜线来说,在O.25 mm(10mil)厚的FR4碾压情况下,位于地线层上方的0.5 mm(20 mil)宽,20 mm(800 mil)长的线能产生9.8 m∧的阻抗,20 nH的电感以及与地之间1.66 pF的耦合电容。将上述值与元器件的寄生效应相比,这些都是可以忽略不计的,但所有布线的总和可能会超出寄生效应。因此,设计者必须将这一点考虑进去。PCB布线的普遍方针:

(1)增大走线的间距以减少电容耦合的串扰;

(2)平行的布电源线和地线以使PCB电容达到最佳;

(3)将敏感的高频线布在远离高噪声电源线的地方;

(4)加宽电源线和地线以减少电源线和地线的阻抗。

2.2 分割

分割是指用物理上的分割来减少不同类型线之间的耦合,尤其是通过电源线和地线。

图2给出了用分割技术将4个不同类型的电路分割开的例子。在地线面,非金属的沟用来隔离四个地线面。L和C作为板子上的每一部分的过滤器.减少不同电路电源面间的耦合。高速数字电路由于其更高的瞬时功率需量而要求放在电源入口处。接口电路可能会需要静电释放(ESD)和暂态抑制的器件或电路。对于L和C来说,最好使用不同值的L和C,而不是用一个大的L和C,因为这样它便可以为不同的电路提供不同的滤波特性。

2.3 局部电源和IC间的去耦

局部去耦能够减少沿着电源干线的噪声传播。连接着电源输入口与PCB之间的大容量旁路电容起着一个低频脉动滤波器的作用,同时作为一个电势贮存器以满足突发的功率需求。此外,在每个IC的电源和地之间都应当有去耦电容.这些去耦电容应该尽可能的接近引脚。这将有助于滤除IC的开关噪声。

2.4 接地技术

接地技术既应用于多层PCB,也应用于单层PCB。接地技术的目标是最小化接地阻抗,以此减少从电路返回到电源之间的接地回路的电势。

(1)单层PCB的接地线

在单层(单面)PCB中,接地线的宽度应尽可能的宽,且至少应为1.5 mm(60 mil)。由于在单层PCB上无法实现星形布线,因此跳线和地线宽度的改变应当保持为最低,否则将引起线路阻抗与电感的变化。

(2)双层PCB的接地线

在双层(双面)PCB中,对于数字电路优先使用地格栅/点阵布线,这种布线方式可以减少接地阻抗,接地回路和信号环路。像在单层PCB中,地线和电源线的宽度最少应为1.5 mm。另外的一种布局是将接地层放在一边,信号和电源线放于另一边。在这种布置方式中将进一步减少接地回路和阻抗,去耦电容可以放置在距离IC供电线和接地层之间尽可能近的地方。

(3)保护环

保护环是一种可以将充满噪声的环境(比如射频电流)隔离在环外的接地技术,这是因为在通常的操作中没有电流流过保护环。

(4)PCB电容

在多层板上,由分离电源面和地面的绝缘薄层产生了PCB电容。在单层板上,电源线和地线的平行布放也将导致这种电容效应。PCB电容的一个优点是它具有非常高的频率响应和均匀的分布在整个面或整条线上的低串连电感。它等效于一个均匀分布在整个板上的去耦电容。没有任何一个单独的分立元件具有这个特性。

(5)高速电路与低速电路

布放高速电路时应使其更接近接地面,而低速电路应使其接近电源面。

(6)地的铜填充

在某些模拟电路中,没有用到的电路板区域是由一个大的接地面来覆盖,以此提供屏蔽和增加去耦能力。但是假如这片铜区是悬空的(比如它没有和地连接),那么它可能表现为一个天线,并将导致电磁兼容问题。

(7)多层PCB中的接地面和电源面

在多层PCB中,推荐把电源面和接地面尽可能近的放置在相邻的层中,以便在整个板上产生一个大的PCB电容。速度最快的关键信号应当临近接地面的一边,非关键信号则布放为靠近电源面。

(8)电源要求

当电路需要不止一个电源供给时,采用接地将每个电源分离开。但是在单层PCB中多点接地是不可能的。一种解决方法是把从一个电源中引出的电源线和地线同其他的电源线和地线分隔开。这同样有助于避免电源之间的噪声耦合。

3 结束语

本文所介绍的各种方法与技巧有利于提高PCB的EMC特性,当然这些只是EMC设计中的一部分,通常还要考虑反射噪声,辐射发射噪声,以及其他工艺技术问题引起的干扰。在实际的设计中,应根据设计的目标要求和设计条件,采用合理的抗电磁干扰措施,设计出具有良好EMC性能的PCB电路板。

PCB 电路 电子 集成电路 EMC 电容 电感 电流 滤波器 射频 模拟电路 相关文章:

- Cadence 推出创新的FPGA-PCB协同设计解决方案(04-25)

- 高速PCB布线实践指南(11-01)

- PCB抄板/设计原理图制成PCB板的过程经验(02-04)

- IBIS 模型:利用 IBIS 模型研究信号完整性问题(08-08)

- 巧妙的线路板布线改善蜂窝电话的音质(11-01)

- PCB反设计系统中的探测电路(02-18)