布线工程师如何充分掌控时钟信号?

在数字电路设计中,时钟信号是一种在高态与低态之间振荡的信号,决定着电路的性能。在应用中,逻辑可能在上升沿、下降沿触发,或同时在上升沿和下降 沿触发。由于溢出给定时钟域的案例极多,故有必要插入缓冲器树来充足地驱动逻辑。时钟树通常带有布线工程师必须满足的延迟、歪曲率、最小功率及信号完整性 要求。

当电路从前工序设计人员转移到后工序布线工程师时,可以认为时钟概述与图表是必须沟通的最关键信息。多年以来,由于沟通失误,数以小时、天甚至是星期计的设计工作沦为白费,需要包括时钟树在内的全套重新合成。

在布线之前,采用极佳的时钟来用于合成及时序约束。约束的时钟定义可能出现在模块的顶层焊盘或引脚;可能出现在宏的输出,如锁延迟环(DLL) 或锁相环(PLL);或者作为产生的时钟出现在除法寄存器上。这些时钟定义可能是也可能不是布线工程师需要定义时钟树根以在不同工作模式之间获得最优延迟 及平衡歪曲率的领域。前工序及布线工程师之间围绕这些信息的高级别信息沟通以及理解布线工程师怎样运用这些信息,将大幅优化物理设计流程的CTS过程。

有效CTS的设计技巧

下面的某些技巧在业界已经使用多年,但基于过去几年的经验,仍然值得重复运用。

为时钟树根使用中到大强度的驱动器。这就使时钟树能有恰当的起点。但不要使用库中最大的驱动强度,如果信号完整性(SI)分析或片上变化(VOC)分析未出现问题,能够在随后的设计中用到。

如果时钟除法寄存器及其同步寄存器要在单独测试模式中工作,确保它们被复用逻辑有针对性地驱动。这就能够在测试模式下在输入端增加延迟,而不会影响此功能模式下所产生的时钟驱动的其他所有寄存器。

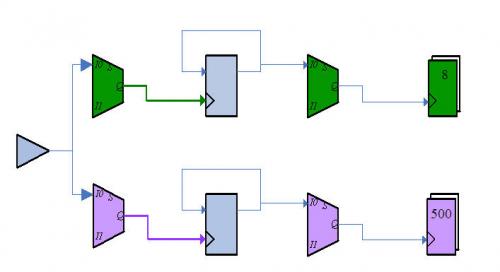

(divide-by)寄存器不会与任何下行寄存器平衡。绿色域的寄存器数量越少,越会使时钟速度比紫色域中的时钟速度快得多。

图1 寄存器时钟除法寄存器

图2显示了可能使每簇下行寄存器及除法寄存器能够通过复用的一种输入拥有极小时钟及通过复用的另一路输入拥有平衡时钟的复用机制。

图2 下行寄存器及除法寄存器复用机制

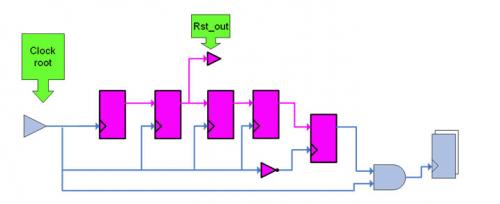

若有需要,则插入专用复位驱动器。某些情况下将使用几个寄存器来同步复位。那些寄存器可能并不需要由相同的寄存器来平衡。在图3中,由于未采用集中策略,软件将尝试平衡门控逻辑后的蓝色寄存器,而每个粉红色寄存器包含在复位同步逻辑中。

图3 平衡门控逻辑后的寄存器

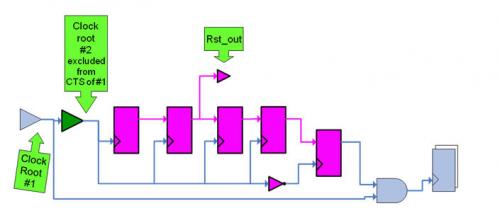

如果它们在各自专用驱动器中与其他寄存器分开了的话,在布线过程中这种情况就很容易处理。图4显示了可以怎样在设计交递(hand-off)沟通过程中插入及轻易识别占位符(place-holder)或排除缓冲器,使布线工程师知道哪里可能会出现平衡问题。

图4 插入及轻易识别占位符或排除缓冲器

提供超出预期的时钟图表及大量时钟简介。当前工序设计准备好提供网表进行布线时,他们已经非常熟悉设计及时钟要求。某些情况下,初始CTS设计 会提示预布线时序约束中使用的理想值在实际物理设计中不能实现的情况。如果提供了精确的时钟图以及带有时钟原理相关信息的网表交递,就能够更快地弄清导致 此状况的问题。

总体图或是代表设计中所有时钟(含门控逻辑)的图非常有用。这要么是采用画图软件,要么是使用电路图捕获工具等使用软件产生的图,甚至还可以是手绘并存储为PDF文档或发送传真给布线工程师的图。此图抵得上尝试直接获得时钟格式的多次通话或电子邮件沟通过程中的千言万语。

由于图表可能会很复杂繁琐,就需要提供相应的简介文档,包括产生的时钟、任何时钟门控或复用图案的详情以及歪曲率平衡和延迟要求等方面的阐释。 每种工作模式都需要这些详细信息,因为在插入时钟树期间必须应对每种模式。寄存器可能最后会提供用于功能模式的平衡,但如果我们不仔细的话,测试模式下可 能极不平衡。

如果时钟使用DLL或其他宏或它通过门控逻辑,这些详细信息就在所必需了。如果有需要的话,有可能通过那些类型的宏来合成及平衡。对于门控逻辑 而言,如果存在一个引脚通过一种模式来连接、但同单元的其他引脚采用另一种模式来连接的情况,走线工具将把这种情况识别为"重汇聚时钟"。虽然布线工具可 以解决这些问题,但更好的解决办法可能是迫使工具在时间插入期间查看这个引脚而非其他引脚。

业界软件工具中的CTS

业界软件遵循设计人员的规格及指引,以强大的工具推动时钟树合成。源自前工序的跟时钟树根插入点、延迟、歪曲率及过渡目标相关的信息以及用于门 控逻辑、通过寄存器和跨域关系的详细信息能够直接移

- 高速PCB布线实践指南(11-01)

- Cadence布线常见问题(11-12)

- 高速PCB设计中的常见问题及解决方法(07-22)

- PROTEL99SE PCB中有多个完全相同的电路块时设计方法(07-13)

- protel技术大全 学习protel常见问题汇总(07-22)

- 实现PCB高效自动布线的设计(07-20)