晶圆芯片级封装(WCSP)在克服各种挑战的同时不断发展

时间:02-14

来源:互联网

点击:

作者:David Stepniak、Craig Beddingfield、Chris Manack 以及 Rajiv Dunne,德州仪器 (TI)

晶圆芯片级封装 (WCSP) 去掉了许多传统的封装步骤,例如:裸片焊接、引线接合以及芯片级倒装片 (flip chip) 连接工艺等。这种方法使半导体客户加速了产品上市进程。WCSP应用正扩展到一些新领域,并逐渐出现基于引脚数量和器件类型的细分市场。集成无源分立RF和存储器件的WCSP应用也正扩展到逻辑IC和MEMS。但是这种发展也带来了许多挑战,包括裸片尺寸和引脚数的增长对板级可靠性所产生的影响。本文将介绍我们当前面临的诸多挑战,以及集成化和硅过孔 (TSV) 技术等一些未来发展趋势。

WCSP在过去十年获得了长足的发展,已成为主要尺寸封装之一。WCSP专业技术公司已经从一些小公司发展成为大型封装分包商,以及一些拥有150mm、200mm和300mm 制造能力(制造能力和赶超能力需求迅速增长)的大型集成器件厂商。由于早期的一些用户集成了无源器件和分立器件,使应用空间也获得了相当大的增长。

由于WCSP已经发展成熟,大型裸片和器件类型变得多样化。在整个发展过程中,始终保留着一个关键属性:在不使用倒装片底层填充 (underfill) 的情况下获得可靠性(限制裸片尺寸)。

焊球间距始终主要为0.5mm,而大批量生产时仍为0.4mm。0.3mm的凸焊能力已得到证明,但其采用受到安装表面贴装技术 (SMT) 工具集功能、基板成本以及倒装片底层填充潜在需求的阻碍。

材料组合以及对工艺条件的理解能力都已得到提高。这些反过来又支持更高的可靠性,以及敏感器件更低的固化温度,例如:存储器等。

为什么采用WCSP?

WCSP具有许多优点,包括封装尺寸缩小、更低的成本、更高的电气性能以及比传统封装相对简单的结构等。相比倒装片板上组件,WCSP器件一般不要求倒装片底层填充。实际上,已经得到证明的是:0.4mm最小焊球间距和126引脚数的WCSP器件并不需要使用倒装片底层填充来满足板级可靠性要求。随着WCSP尺寸和引脚数的不断增加,这一优点也受到了挑战,但如果使用了正确的协同设计策略这种优点仍然可以保留。由于WCSP向0.3mm焊球间距转移,很可能会要求使用倒装片底层填充来确保满足板级可靠性要求。尽管拥有很多优势,但也存在众多挑战——最明显的便是可靠性和设计挑战。

挑战

相当多的研究已经帮助克服了这些挑战,而WCSP封装已在许多新的器件类型和应用得到应用。除可靠性和设计挑战以外,其他主要的挑战还包括测试和晶圆处理。未来的一些机遇(包括3D/TSV)将带来更多的挑战,从而需要创新型解决方案。

板级可靠性。一般而言,板级可靠性 (BLR) 测试包括温度周期变化、压降测试和弯曲测试。但是了解对组件应用可靠性的影响也很重要,包括使用实例和贴装结构(贴装至印刷线路板 (PWB) 层压板模块还是陶瓷模块)。焊盘过孔和非焊盘过孔混合结构使用的一些模块应用在获得 BLR 方面最为困难。但是,我们可以使用一些协同设计策略来提高 BLR 性能,包括层叠结构、智能焊球数量减少以及独特的重新分布层 (RDL) 设计。

由于移动设备厂商压低其印刷电路板 (PCB) 上无源组件的高度,半导体供应商也同步降低了封装高度。结果,随着焊料基准距的减小,板级温度周期性能也被降低,因为硅和PCB材料之间热膨胀的错配系数。在低引脚数模拟器件中,例如:音频放大器等,这些整体应力并不是一个大问题。但是,随着器件功能增加以及更多组件集成到同一块硅片中,最远焊球DNP(到中性点的距离)会更大,从而增加BLR风险。

新一代WCSP将侧重于封装的掩模组减少。掩模减少,可以实现更短的产品上市时间和更低的封装成本。但是,必须要在不牺牲电迁移和BLR的情况下实现这种转变。在WCSP中,我们习惯上认为最必需的一层是凸块底部金属层,其会减缓焊料中锡和RDL之间的反应。进一步来说,扩散阻隔层将会与重分布层混合,从而除去UBM层。

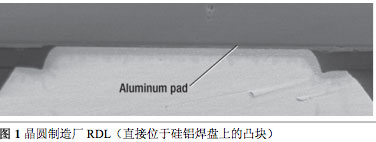

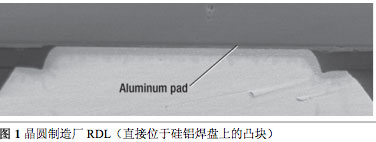

设计。WCSP供应商在从焊盘到区域阵列范围 (area array pattern) 的什么地方构建布线所需的RDL存在争议。晶圆加工厂方法(请参见图1)中,通常将一个额外增加的铝层用于这种连接。这种方法的缺点是凸块支持会占用很多的顶层金属面积。

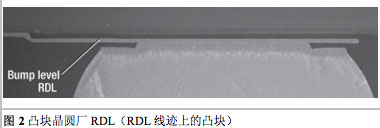

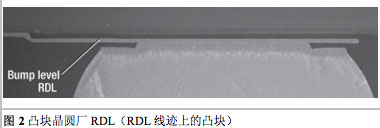

最常见是使用铜的凸块晶圆厂RDL(请参见图2)方法。这种方法具有更高的电流密度和可靠性,因为可以使用更厚的电介质和金属层。凸块晶圆厂RDL还允许将出货晶圆分成不同的封装类型,包括传统的引线接合封装或者WCSP,其为产品开发阶段理想的选择,因为可以很容易地生产电气特性的快速批量样片。相同器件可以使用不同方法时,客户会根据散热额定值、单价以及最适合其应用的尺寸来选择某种封装。未来,随着晶圆厂采用一些创新型铜工艺解决方案/结构,并增加更厚的电介质容量,业界对于从单独凸焊厂向晶圆厂转移的这一过程可能会进行重新评估。

另一个重要的挑战是了解RDL布局对RF性能的影响。作为协同设计努力的一个部分,IC处于平面布局说明时就必须对RDL进行设计,旨在优化器件性能。另外,必须遵循一种结构化的协同设计方法,以保证电气性能和机械可靠性,因为组件焊球的位置也在平面布局期间确定。多种封装配置(WCSP、引线接合BGA、倒装片BGA)中相同硅设计的使用,也可以在结构化协同设计尝试期间确定。

随着硅节点的技术进步以及裸片尺寸的缩小,我们必须注意其他一些挑战。我们必须理解低介电常数 (low-k) 电介质的WCSP完整性、划片街区 (saw streets) 宽度减少以及多个晶圆厂和组装厂的整合,目的是确保WCSP封装的完整性和可靠性得到维持。

晶圆芯片级封装 (WCSP) 去掉了许多传统的封装步骤,例如:裸片焊接、引线接合以及芯片级倒装片 (flip chip) 连接工艺等。这种方法使半导体客户加速了产品上市进程。WCSP应用正扩展到一些新领域,并逐渐出现基于引脚数量和器件类型的细分市场。集成无源分立RF和存储器件的WCSP应用也正扩展到逻辑IC和MEMS。但是这种发展也带来了许多挑战,包括裸片尺寸和引脚数的增长对板级可靠性所产生的影响。本文将介绍我们当前面临的诸多挑战,以及集成化和硅过孔 (TSV) 技术等一些未来发展趋势。

WCSP在过去十年获得了长足的发展,已成为主要尺寸封装之一。WCSP专业技术公司已经从一些小公司发展成为大型封装分包商,以及一些拥有150mm、200mm和300mm 制造能力(制造能力和赶超能力需求迅速增长)的大型集成器件厂商。由于早期的一些用户集成了无源器件和分立器件,使应用空间也获得了相当大的增长。

由于WCSP已经发展成熟,大型裸片和器件类型变得多样化。在整个发展过程中,始终保留着一个关键属性:在不使用倒装片底层填充 (underfill) 的情况下获得可靠性(限制裸片尺寸)。

焊球间距始终主要为0.5mm,而大批量生产时仍为0.4mm。0.3mm的凸焊能力已得到证明,但其采用受到安装表面贴装技术 (SMT) 工具集功能、基板成本以及倒装片底层填充潜在需求的阻碍。

材料组合以及对工艺条件的理解能力都已得到提高。这些反过来又支持更高的可靠性,以及敏感器件更低的固化温度,例如:存储器等。

为什么采用WCSP?

WCSP具有许多优点,包括封装尺寸缩小、更低的成本、更高的电气性能以及比传统封装相对简单的结构等。相比倒装片板上组件,WCSP器件一般不要求倒装片底层填充。实际上,已经得到证明的是:0.4mm最小焊球间距和126引脚数的WCSP器件并不需要使用倒装片底层填充来满足板级可靠性要求。随着WCSP尺寸和引脚数的不断增加,这一优点也受到了挑战,但如果使用了正确的协同设计策略这种优点仍然可以保留。由于WCSP向0.3mm焊球间距转移,很可能会要求使用倒装片底层填充来确保满足板级可靠性要求。尽管拥有很多优势,但也存在众多挑战——最明显的便是可靠性和设计挑战。

挑战

相当多的研究已经帮助克服了这些挑战,而WCSP封装已在许多新的器件类型和应用得到应用。除可靠性和设计挑战以外,其他主要的挑战还包括测试和晶圆处理。未来的一些机遇(包括3D/TSV)将带来更多的挑战,从而需要创新型解决方案。

板级可靠性。一般而言,板级可靠性 (BLR) 测试包括温度周期变化、压降测试和弯曲测试。但是了解对组件应用可靠性的影响也很重要,包括使用实例和贴装结构(贴装至印刷线路板 (PWB) 层压板模块还是陶瓷模块)。焊盘过孔和非焊盘过孔混合结构使用的一些模块应用在获得 BLR 方面最为困难。但是,我们可以使用一些协同设计策略来提高 BLR 性能,包括层叠结构、智能焊球数量减少以及独特的重新分布层 (RDL) 设计。

由于移动设备厂商压低其印刷电路板 (PCB) 上无源组件的高度,半导体供应商也同步降低了封装高度。结果,随着焊料基准距的减小,板级温度周期性能也被降低,因为硅和PCB材料之间热膨胀的错配系数。在低引脚数模拟器件中,例如:音频放大器等,这些整体应力并不是一个大问题。但是,随着器件功能增加以及更多组件集成到同一块硅片中,最远焊球DNP(到中性点的距离)会更大,从而增加BLR风险。

新一代WCSP将侧重于封装的掩模组减少。掩模减少,可以实现更短的产品上市时间和更低的封装成本。但是,必须要在不牺牲电迁移和BLR的情况下实现这种转变。在WCSP中,我们习惯上认为最必需的一层是凸块底部金属层,其会减缓焊料中锡和RDL之间的反应。进一步来说,扩散阻隔层将会与重分布层混合,从而除去UBM层。

设计。WCSP供应商在从焊盘到区域阵列范围 (area array pattern) 的什么地方构建布线所需的RDL存在争议。晶圆加工厂方法(请参见图1)中,通常将一个额外增加的铝层用于这种连接。这种方法的缺点是凸块支持会占用很多的顶层金属面积。

最常见是使用铜的凸块晶圆厂RDL(请参见图2)方法。这种方法具有更高的电流密度和可靠性,因为可以使用更厚的电介质和金属层。凸块晶圆厂RDL还允许将出货晶圆分成不同的封装类型,包括传统的引线接合封装或者WCSP,其为产品开发阶段理想的选择,因为可以很容易地生产电气特性的快速批量样片。相同器件可以使用不同方法时,客户会根据散热额定值、单价以及最适合其应用的尺寸来选择某种封装。未来,随着晶圆厂采用一些创新型铜工艺解决方案/结构,并增加更厚的电介质容量,业界对于从单独凸焊厂向晶圆厂转移的这一过程可能会进行重新评估。

另一个重要的挑战是了解RDL布局对RF性能的影响。作为协同设计努力的一个部分,IC处于平面布局说明时就必须对RDL进行设计,旨在优化器件性能。另外,必须遵循一种结构化的协同设计方法,以保证电气性能和机械可靠性,因为组件焊球的位置也在平面布局期间确定。多种封装配置(WCSP、引线接合BGA、倒装片BGA)中相同硅设计的使用,也可以在结构化协同设计尝试期间确定。

随着硅节点的技术进步以及裸片尺寸的缩小,我们必须注意其他一些挑战。我们必须理解低介电常数 (low-k) 电介质的WCSP完整性、划片街区 (saw streets) 宽度减少以及多个晶圆厂和组装厂的整合,目的是确保WCSP封装的完整性和可靠性得到维持。

德州仪器 半导体 MEMS 电路 PCB 放大器 电流 自动化 CMOS 传感器 电子 相关文章:

- IBIS 模型:利用 IBIS 模型研究信号完整性问题(08-08)

- IBIS模型:利用IBIS模型研究信号完整性问题(09-08)

- 挠性电路材料(12-10)

- 详解最新PCB冷却技术(12-17)

- 元件封装基本知识(02-10)

- PCB板返修时的两个关键工艺(03-04)