静噪教程系列之噪声问题复杂化的因素(一)

要应对电子设备噪声干扰,不仅需要了解噪声源,还必须知晓传输路径和天线的特征。本章节详细介绍了其中的传输路径。

在此之前,已经通过较为简单的表述解释了噪声的产生(谐波除外)。但是,在解释噪声传输和发射的机制时,会提及传输理论、电磁学和天线理论中使用的术语(如图3-1-1所示)。如果不理解这些术语,就无法处理噪声问题。

因此,本章节将(尽量使用较少的公式)解释这些术语,并介绍关于噪声的重要课题,如谐振和阻尼、噪声传导和反射以及源阻抗。

图1 本章将要介绍的内容

1. 谐振和阻尼

在产生噪声或接收到噪声感应时,谐振是一个重要因素。如果电路中包含意外建立的谐振电路,则会在谐振频率处产生非常大的电流或电压,更易产生噪声干扰。尽可能消除电路中的谐振是很重要的。如果要抑制谐振,需使用阻尼电阻器。本章节将介绍谐振和阻尼电阻器。

1. 1并联谐振和串联谐振

(1) LC谐振电路

谐振指的是电路中的感应电抗和电容电抗在特定频率处相互抵消,这个特定频率就叫做“谐振频率”。尽管能产生电抗(阻抗的虚数分量)的典型元件是电感器 (线圈) 和电容器,但任何其他元件,甚至连简单的导线都可以是产生谐振的要素,因为它们仍具有非常小的电抗。(尽管除上述元件之外,天线、平行板、传输路径等也可能导致与EMC相关的谐振,但此处我们只着重于电感器和电容器产生的LC谐振。)

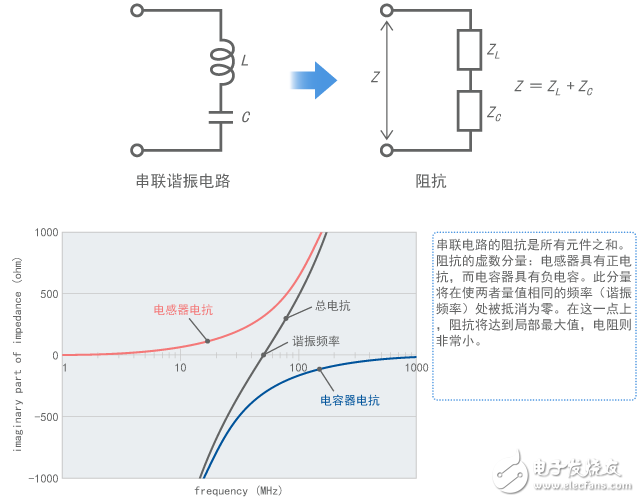

(2) 谐振电路的阻抗

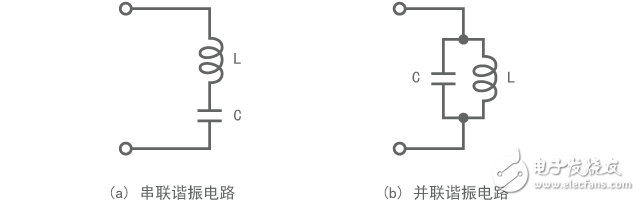

如图2所示,谐振电路分两种: 串联谐振和并联谐振。根据图3-2-2中的计算示例,串联谐振使阻抗降至最低值(理论上为零),而并联谐振使阻抗升到最高值(理论上为无穷大)。

图2 串联谐振和并联谐振

(该图表示电抗在数轴上的大小)

图3 谐振电路的阻抗

(3) 电抗抵消为零

如图3-2-3所示,电感器电抗和电容器电抗的量值在谐振频率处变为相等,两者相互抵消,最终相加之和为零。

图3-2-3解释了串联谐振的情形;如果是并联谐振,则将电抗替换为电纳(导纳的虚数成分),会出现电纳在谐振频率处被抵消为零。因此,阻抗升到最高值,这很容易理解。

(4) 谐振频率

无论是串联谐振还是并联谐振,都可以通过以下公式估算出谐振频率ƒ0。在图3-2-2的示例中,ƒ0约为50MHz。

(5) 谐振Q

谐振强度可通过指数Q(质量因子)来表示。Q越高表示谐振越强。指数Q也是用作表示电容器和电感器性能的指数。存在这样一种关系: 当使用Q值较大的电容器或电感器时,所建立谐振电路的Q值也较大。如何估算Q值将在章节3-2-5中作解释。

(6) 电容器和电感器的自谐振

在高频范围内使用电容器或电感器时,由于其固有的寄生成分,电容器或电感器本身会在特定频率处导致谐振。这就叫做自谐振。自谐振将在第6章中进一步讲述。

图4 串联谐振使阻抗降至最低值的机制

- 利用电波暗室测试电路的RF噪声抑制(04-16)

- 汽车电磁噪声抑制干扰电波的设计(06-07)

- LTE供电设备的噪声抑制技术及EMC对策元器件的选择(03-24)

- 降低噪声与电磁干扰的24个窍门(05-20)

- 确保EMC高性能:利用无扼流圈收发器简化CAN总线(10-05)

- Molex推出第二代HOZOX HF2 EMI噪声抑制片(07-29)