很多新手工程师在设计开关电源计算变压器时遇到这些问题怎么解决?

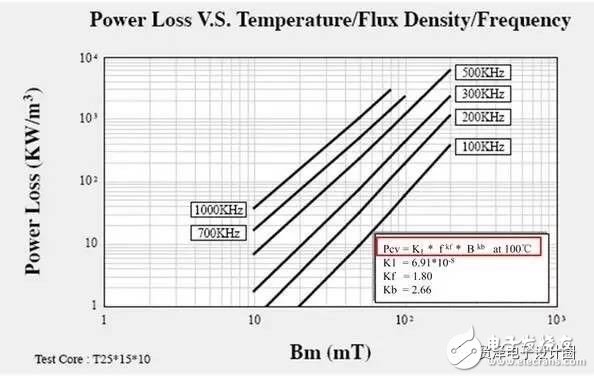

了变压器的转换效率,导致变压器温升高,从而限制开关频率提高。

题主提到了软开关,没错,软开关确实是解决开关损耗的有力手段。而在各种研究软开关的paper上,提出了无数种让人眼花缭乱的软开关方案,似乎软开关能解决一切问题。但是实际工程应用和理论分析不同,实际工程追求的是低成本,高效率,高可靠性,那些需要添加一堆辅助电路,或者要非常精确控制的软开关方案在实际工程中其实都是不太被看好的,所以即使到现在,在工业界最常应用软开关的拓扑也只要移相全桥和一些谐振的拓扑(比如LLC),至于题主提到的flyback,没错,我也听说过有准谐振的flyback(但没研究过),但即使有类似的方案,对于能不能真正工程应用,题主也需要从我上面提到的几个问题去考量一下。

ps,对于小功率高频电源,现在class E非常火,我觉得它火的原因就是电路简单,所以才能被工业界接受,题主有兴趣可以去研究下。

5、高频化带来的一系列问题假设上面的一系列问题都解决了,真正做到高频化还需要解决一系列工程上的问题,比如在高频下,电路的寄生参数往往会严重影响电源的性能(如变压器原副边的寄生电容,变压器的漏感,PCB布线之间的寄生电感和寄生电容等等),造成一系列电压电流波形震荡和EMI的问题,如何消除寄生参数的影响,甚至进一步地,如何利用寄生参数为电路服务,都是有待研究的问题。

ps,对于高频化应用的实际工程应用的问题,还有很重要的一块是高频驱动电路的设计。

当然,随着新器件(SiC, GaN)的兴起,开关电源高频化的研究方兴未艾,开关电源的高频化一定是趋势,而且有望给电力电子带来又一次革命。让我们拭目以待。

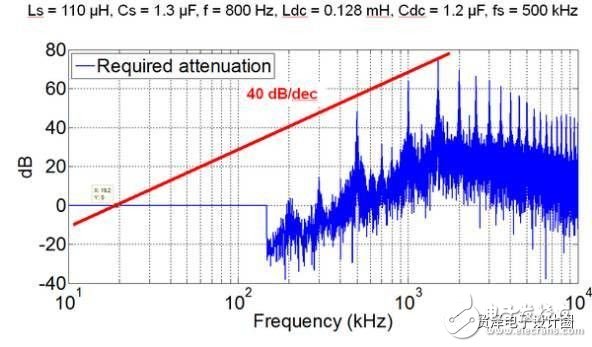

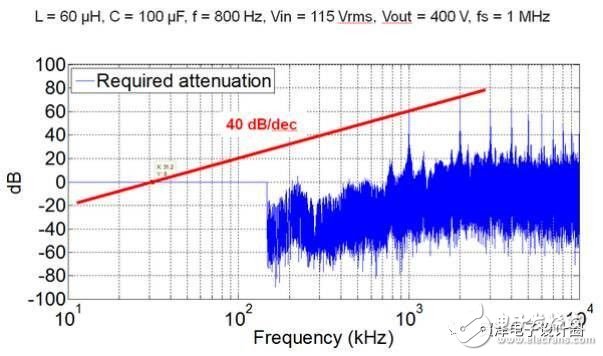

6、EMI和干扰,PCB布局难度增大在我接触EMI前,很多老工程师以他们有丰富的EMI调试经验来鄙视我们这些菜鸟,搞的我一直以为EMI是门玄学,也有很多人动不动就拿EMI出来吓人。我想说EMI确实很难理解,很难有精确的纸面设计,但是通过研究我们还是能知道大概趋势指导设计,而不是一些工程嘴里完全靠trial and error的流程。我先给出结论,EMI确实和开关频率不成线性关系,某些开关频率下,EMI滤波器的转折频率较高,但是总体趋势而言,是开关频率越高,EMI体积越小!

我知道很多人可能开始喷我了,怎么可能,di/dt和dv/dt都大了,怎么可能EMI滤波体积还小了。我想说一句,共模和差模滤波器的没有区别,相同的截止频率下,高频的衰减更大!就算你高频下共模噪声越大,但是你的记住,这个频率下LC滤波器的衰减更大,想想幅频曲线吧。为了说明这个结论,我给出一些定量分析结果。这些EMI分析均基于AC/DC三相整流,拓扑为维也纳整流。我分别给出了1Mhz和500Khz的共模噪声,可以看出,500khz共模滤波器需要的截止频率为19.2kHz,1MHz为31.2kHz。

假设上述的功率器件损耗解决了,真正做到高频还需要解决一系列工程问题,因为在高频下,电感已经不是我们熟悉的电感,电容也不是我们已知的电容了,所有的寄生参数都会产生相应的寄生效应,严重影响电源的性能,如变压器原副边的寄生电容、变压器漏感,PCB布线间的寄生电感和寄生电容,会造成一系列电压电流波形振荡和EMI问题,同时对开关管的电压应力也是一个考验。

7、小结不是开关频率越高,功率密度就越高,目前这个阶段来说真正阻碍功率密度提高的是散热系统和电磁设计(包括EMI滤波器和变压器)和功率集成技术。

慎重选择开关频率,开关频率会极大的影响整个变化器的功率密度,而且针对不同器件,拓扑,最佳的开关频率是变化的。

高频确实产生很多很难解决的干扰问题,往往要找到干扰回路,然后采取一些措施。

为了继续维持电力电子变换器功率密度的增长趋势,高频肯定是趋势。只是针对高频设计的电力电子技术很不成熟,相关配套芯片没有达到要求,一些高频的电磁设计理论不完善和精确,使用有限元软件分析将大大增加开发周期。

要提高开关电源产品的功率密度,首先考虑的是提高其开关频率,能有效减小变压器、滤波电感、电容的体积,但面临的是由开关频率引起的损耗,而导致温升散热设计难,频率的提高也会导致驱动、EMI等一系列工程问题。

- EMI噪声分析及EMI滤波器的设计(10-07)

- 开关电源的EMC设计(09-15)

- 多层线路板在开关电源电路中应用(11-07)

- 双激式开关电源变压器存在的风险(01-20)

- 开关电源的分类及应用(02-17)

- 开关电源控制环路如何设计(04-11)