很多新手工程师在设计开关电源计算变压器时遇到这些问题怎么解决?

引言

估计很多新手工程师在设计开关电源计算变压器时发现,把电源的开关频率提高后变压器磁芯更加不容易饱和,或者说可以用更小的磁性做出同样功率的电源,甚至在想把开关频率无限制提高来无限制缩小变压器的体积。

但实际上一般开关电源的频率都不会特别高,也不可能使频率无限提高,其中到底有哪些原因?请看下文!

器件限制、损耗、EMI、PCB布局难度提升等问题都是制约开关频率无限提升的因素,下面稍微展开来讲一下!

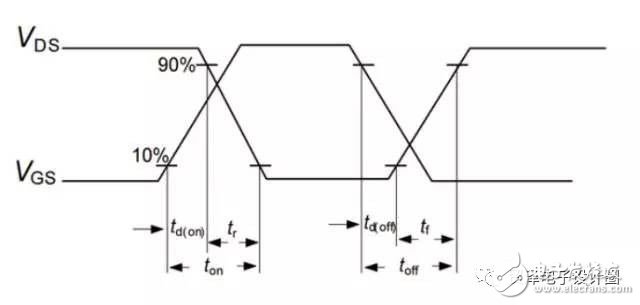

1、器件的限制对于一个开关管来说,在实际应用中,不是给个驱动就开,驱动撤掉就关了。它有开通延迟时间(td(on)),上升时间(tr),关断延迟时间(td(off)),下降时间tf,对应的波形如下:

通俗的讲,开关管开通关断不是瞬间完成的,需要一定的时间,开关管本身的开关时间就限制了开关频率的提升。

曾经笔者在delta用在3kW的逆变器上的一款600V的coolmos为例。看看这些具体的开关时间是多少

那么对于这个mos管来说,它的极限开关频率(在这种极限情况下,mos管刚开通就关断)fs=1/(16+12+83+5)ns=8.6MHz,当然,在实际应用中,由于要调节占空比,不可能让开关管一开通就关断,所以实际的极限频率是远低于8.6MHz的,所以器件本身的开关速度是限制开关频率的一个因素。

2、开关损耗当然,随着器件的进步,开关管开关的速度越来越快,尤其是在低压小功率场合,如果仅考虑器件本身的开关速度,开关频率可以run得非常高,但实际并没有,限制就在开关损耗上面。

图下面给出开关管实际开通的时候对应的波形图

可以看到,开关管每开通一次,开关管DS的电压(Vds)和流过开关管的电流(Id)会存在交叠时间,从而造成开通损耗,关断亦然。假设每次开关管每开关一次产生的能量损耗是一定的,记为Esw,那么开关管的开关损耗功率就为Psw=Esw*fs,显然,开关频率越高,开关损耗越大。5M开关频率下开关损耗比500K要大10倍,这对于重视效率的开关电源来说,显然是不可接受的。所以,开关损耗是限制开关频率的第二因素。

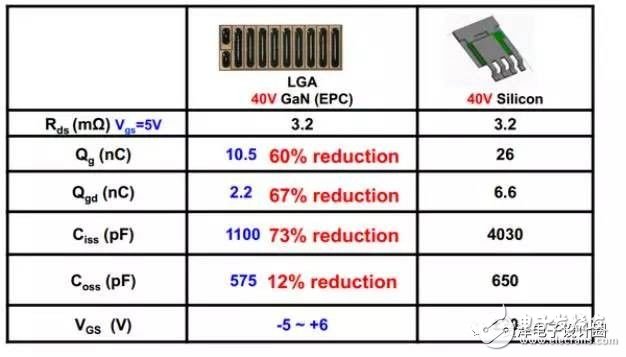

开关损耗确实是限制因素之一,但是氮化镓器件的推出已经让开关损耗在1-3Mhz这个范围内变得可以接受。

下面在贴出一张低压氮化镓和硅器件的比较,可以看出,总体来说,驱动损耗也会变得很小。

还有一点很重要,宽禁带半导体的工作结温很高,以目前的工艺来说,Sic的结温可以工作到200°,氮化镓可以工作到150°。而硅器件呢,我觉得最多100°就不得了。结温高,意味着相同损耗下,需要给宽禁带半导体设计的散热器表面积要小很多,何况宽禁带半导体的损耗本身还小。

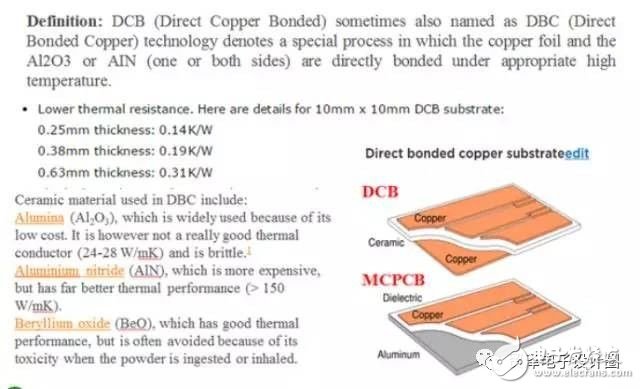

是开关频率的提高,往往只能使用QFN或者其他一些表贴器件减少封装寄生参数,这给散热系统带来了极大的挑战,原来To封装可以加散热器,减少到空气对流的热阻,而现在不行了。所以如果想在高频下工作,第一问题就是解决散热,把高开关损耗导出去,尤其是在kW级别,散热系统非常重要。现在学界解决这个问题的手段偏向于把器件做成独立封装,采用一种叫DCB的技术,用陶瓷基板散热,器件从陶瓷上表面到下表面的热阻基本为0.4°C/W(有些人也用metal core PCB, 但是要加绝缘层,热阻一般在4°C/W),而FR4为20°C/W。

半导体不断在发展,开关损耗也在显著下降,而封装越来越小,现在来看,我们要做的是怎么把那些热量从那么小的表贴封装下散出去。

3、磁元件损耗绕组的趋肤效应和临近效应。在变压器的高频工作时,影响更加严重。会引起较大的绕组涡流耗损,当然开关频率提高,绕组的匝数会降低。相应的绕组交流阻抗变大了,但是绕线长度减少了。问题貌似也不会很大,谐振半桥应用,我们经常会选200KHZ的频率。这样磁性元件的体积和耗损,是一个比较合适的范围。

变压器的铁损主要由变压器涡流损耗产生,如下图所示,给线圈加载高频电流时,在导体内和导体外产生了变化的磁场垂直于电流方向(图中1→2→3和4→5→6)。根据电磁感应定律,变化的磁场会在导体内部产生感应电动势,此电动势在导体内整个长度方向(L面和N面)产生涡流(a→b→c→a和d→e→f→d),则主电流和涡流在导体表面加强,电流趋于表面,那么,导线的有效交流截面积减少,导致导体交流电阻(涡流损耗系数)增大,损耗加大。

如下图所示,变压器铁损是和开关频率的kf次方成正比,又与磁性温度的限制有关,所以随着开关频率的提高,高频电流在线圈中流通产生严重的高频效应,从而降低

- EMI噪声分析及EMI滤波器的设计(10-07)

- 开关电源的EMC设计(09-15)

- 多层线路板在开关电源电路中应用(11-07)

- 双激式开关电源变压器存在的风险(01-20)

- 开关电源的分类及应用(02-17)

- 开关电源控制环路如何设计(04-11)