如何有效解决Zynq-7000 AP SoC PS Efuse 设置的完整性在加电/断电受到影响的问题

的关注点,请查看数据手册中的 PS 重置断言时序要求。

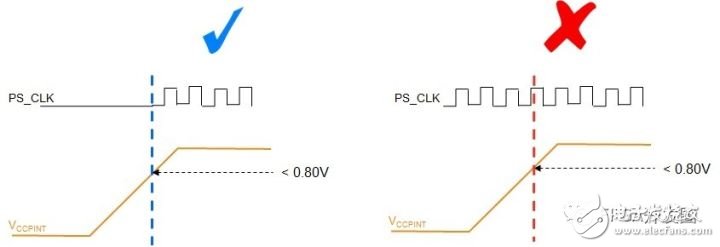

加电解决方案 2:

禁用 PS 参考时钟 (PS_CLK),直到 VCCPINT 高于 0.80V。

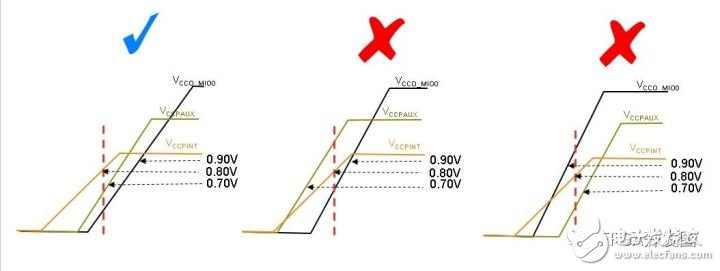

加电解决方案 3:

请遵循数据手册推荐的 PS 加电顺序。

具体而言,为确保 PS eFUSE 完整性,VCCPINT 必须在 VCCPAUX 到达 0.70V 和 VCCO_MIO0 到达 0.90V 之前到达 0.80V。

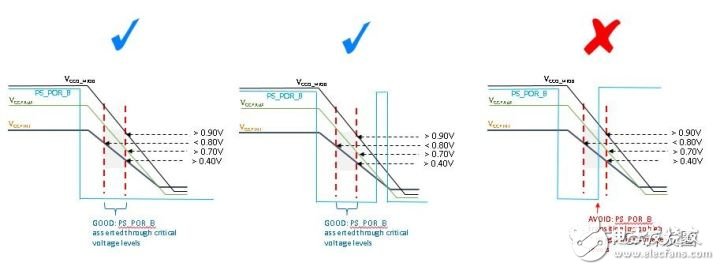

断电解决方案 4:

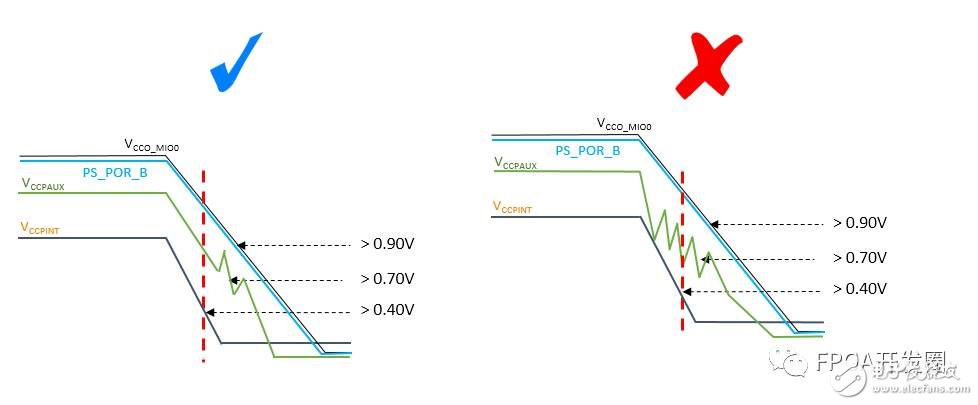

在 VCCPINT 到达 0.80V 之前将 PS_POR_B 断言为 GND,保持断言直至 VCCPINT 低于 0.40V,VCCPAUX 低于 0.70V,或者 VCCO_MIO0 低于 0.90V。

断电解决方案 5:

在 VCCPINT 低于 0.80V 之前,禁用 PS 参考时钟 (PS_CLK)。

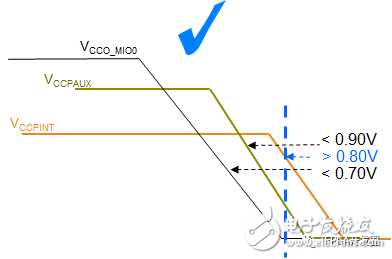

断电解决方案 6:

请遵循数据手册推荐的 PS 断电顺序。

具体而言,为确保 PS eFUSE 完整性,VCCO_MIO0 必须到达 0.90V 或 VCCPAUX 必须达到 0.70V,直至 VCCPINT 到达 0.80V。

断电解决方案 7:

PS_POR_B 保持去断言 (VCCO_MIO0),而且 VCCPINT、 VCCPAUX 和 VCCO_MIO0上的电压斜坡降低保持 无变化,直至至少其中一个电源达到并分别保持在 0.40V、0.70V 和 0.90V 以下。

PVT 考虑:

不论工艺、电压和温度出现任何变化,上述加电和断电条件都必须满足。

VCCPINT、VCCPAUX 和 VCCMIO 的限值描述已考虑各种不同的 PVT 条件。

但用户需要确认 PS_CLK 或 PS_POR_B 上的任何变化不会在不同的 PVT 场景中触发产生故障的条件。

Zynq-7000 相关文章:

- Xilinx多协议机器视觉摄像机参考设计(12-01)

- 基于赛灵思FPGA的端到端广播平台解决方案的实现(10-27)