如何有效解决Zynq-7000 AP SoC PS Efuse 设置的完整性在加电/断电受到影响的问题

描述

在一定条件下,在加电和断电的过程中,Zynq-7000 AP SoC PS Efuse 设置的完整性可能会受到影响。

如果所有下列状况都有发生,则 Zynq-7000 AP SoC PS eFUSE 设置的完整性可能会受到影响:1、推荐的加电和断电顺序未满足2、PS_CLK 在加电和/或断电过程中运行3、在 PS 加电过程中没有按照要求断言 PS_POR_B,或者在断电过程中未断言 PS_POR_B

可能会体现出下列症状:

-

因 RSA 认证的意外启用或不正确的 RSA PPK 散列值所导致的启动失败

-

因意外启用 OCM ROM 128KB CRC 检测导致启动时长超过预期

-

因意外的写保护设置或空白检查错误造成在 PS eFUSE 编程过程中出错

Zynq-7000 AP SoC 设计应该针对给 PS eFUSE 完整性造成的潜在影响进行评估。

请参见以下部分,了解评估潜在影响的方法。

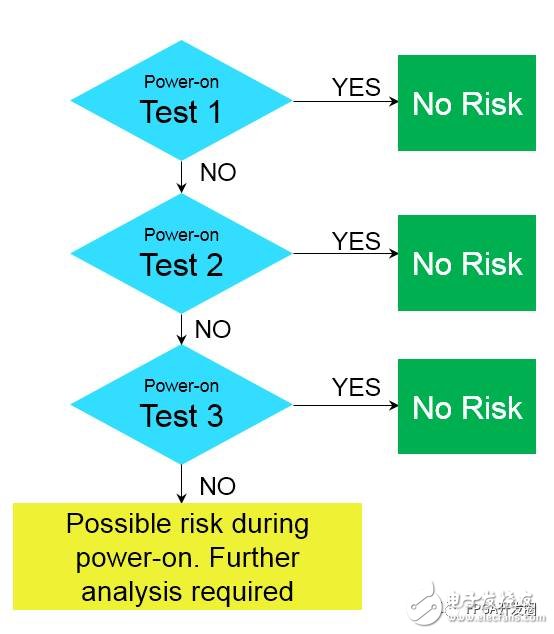

我该如何评估设计在加电过程中是否受到影响?

如果下列所有三个加电测试问题的答案都是否,则 PS eFUSE 完整性可能会在加电过程中受到影响。

请参阅下文中的"何时需要进一步分析"部分。

加电测试 1:PS_POR_B 是否满足数据手册对加电的要求,而且是否在 VCCPINT、VCCPAUX 和 VCCO_MIO0 达到它们的最小电压水平之前 PS_POR_B 断言为低 (GND)?如果是,则无风险。通过该测试即为解决方案 1。

加电测试 2:是否 PS 参考时钟 (PS_CLK) 在 VCCPINT 到达 0.80V 之前处于非活跃状态?如果是,则无风险。通过该测试即为解决方案 2。

加电测试 3:供电顺序是否遵循推荐的加电顺序(1:VCCPINT、2:VCCPAUX、3: VCCO_MIO0)?

VCCPINT 必须在 VCCPAUX 到达 0.70V 以及 VCCO_MIO0 到达 0.90V 之前到达 0.80V。

如果是,则无风险。通过该测试即为解决方案 3。

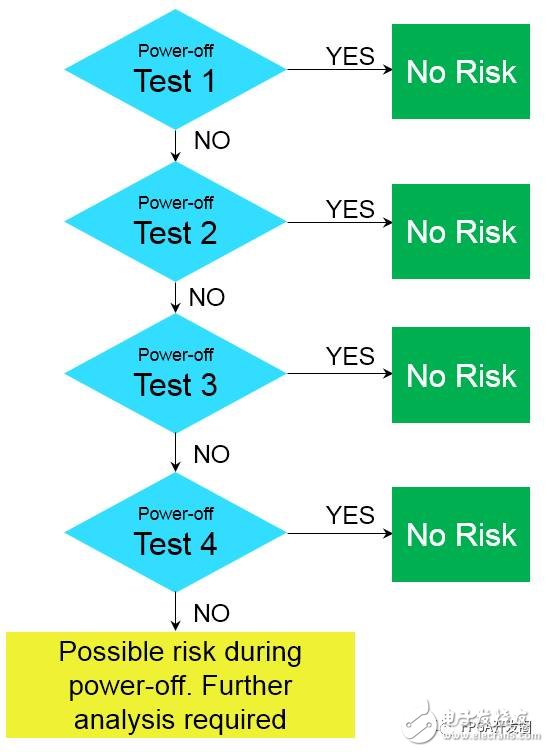

我该如何评估设计是否在断电过程中受到影响?

如果前述所有 4 个断电测试问题的答案都是否,则 PS eFUSE 完整性可能会在断电过程中受到影响。

请参阅下文中的"何时需要进一步分析"部分。

断电测试 1:PS_POR_B 是否在 VCCPINT 到达 0.80V 前断言 (GND) 并保持断言直至 VCCPINT 低于 0.40V 或 VCCPAUX 低于 0.70V 或 VCCO_MIO0 低于 0.90V?

如果是,则无风险。通过该测试即为解决方案 4。

断电测试 2:是否 PS 参考时钟 (PS_CLK) 在 VCCPINT 到达 0.80V 之前处于非活跃状态?

如果是,则无风险。通过该测试即为解决方案 5。

断电测试 3:供电顺序是否遵循推荐的断电顺序(1:VCCO_MIO0、2:VCCPAUX、3:VCCPINT)?也就是说:是否在 VCCPINT 到达 0.80V 之前 VCCO_MIO0 到达 0.90V 或 VCCPAUX 到达 0.70V?

如果是,则无风险。通过该测试即为解决方案 6。

断电测试 4:是否 PS_POR_B 保持去断言 (VCCO_MIO0),而且 VCCPINT、 VCCPAUX 和 VCCO_MIO0 上的电压斜坡下降保持无变化 ,直至至少其中一个电源达到并分别保持在 0.40V、0.70V 和 0.90V 以下?

如果是,则无风险。通过该测试即为解决方案 7。

对于出现了这些症状的系统,我该如何检测 PS eFUSE 完整性?

请参阅下列附件章节,查看能够通过读取 PS eFUSE 阵列判断是否有任何 PS eFUSE 设置与预期设置不同的 XMD 脚本?

请按照附件中 ReadMe.txt 文件的说明进行。

对于现有开发板设计,什么时候需要进一步分析?

关于现有开发板设计的进一步分析,请打开 Xilinx 支持服务请求并准备好提供下列信息:

. 放大加电顺序. 放大断电顺序

-

问题的症状(如果有)。

-

如果观察到有症状存在,您将需要 PS eFUSE 阵列条件(ps_efuse.log 文件)。

-

运行附加的 zynq_efuse_read_normal.zip 实用工具即可得到该信息。查看附件部分。

-

PS_POR_B、VCCPINT、VCCPAUX 以及 VCCO_MIO0的四通道视图。

-

PS_CLK 活动情况与上述一个或多个通道有关的加电及断电视图

为确保 PS eFUSE 完整性而提供的解决方案

有多种解决方案可用于确保 PS eFUSE 的完整性。至少要有一个加电解决方案和一个断电解决方案,才能确保 PS eFUSE 的完整性。

这些解决方案可分为以下类别:

-

在加电(解决方案 1)和断电(解决方案 4)渐变阶段控制 PS_POR_B

-

在加电(解决方案 2)和断电(解决方案 5)渐变阶段控制 PS_POR_B

-

控制加电(解决方案 3)和断电(解决方案 6)顺序

加电解决方案 1:

请满足 PS_POR_B 的数据手册要求。PS_POR_B 在 VCCPINT、VCCPAUX 和 VCCO_MIO0 到达最低工作电压水平前都需要进行断言。

此外,对于相关 (Xilinx 答复 63149)

Zynq-7000 相关文章:

- Xilinx多协议机器视觉摄像机参考设计(12-01)

- 基于赛灵思FPGA的端到端广播平台解决方案的实现(10-27)