教你如何在如何对时钟抖动衰减测试设置

试缩小和扩大BW,然后观察范围内的结果。

假设有一个抖动的输入时钟,你通常应该看到,加宽BW使得输出时钟显示出比输入时钟更小的抖动。这是因为加宽BW意味着PLL将更多的跟踪输入时钟,抖动和其他。在下面的图4中,Si5347的环路宽度已经扩大到4 kHz。基本上没有抖动衰减,与输入时钟相比,输出时钟没有显示出抖动。

相反,缩小BW会使输出时钟与输入时钟相比更加抖动。这是因为较窄的环路BW对应于更多的抖动衰减。具有讽刺意味的是,这种测试配置中的抖动衰减器是非常成功的,这是问题的根本原因。如果输出时钟只是跟踪输入时钟,则触发源将是无关紧要的。在下图中,Si5347的环路宽度被缩小到100 Hz。

抖动衰减时钟通常不同于其抖动输入时钟,高于和超出任何频率缩放。如果其频谱发生明显变化,则在测量和比较每个时钟的相位噪声时应该相对明显。然而,如前所述,这需要专门的设备,如相位噪声分析仪或具有相位噪声选项的频谱分析仪。

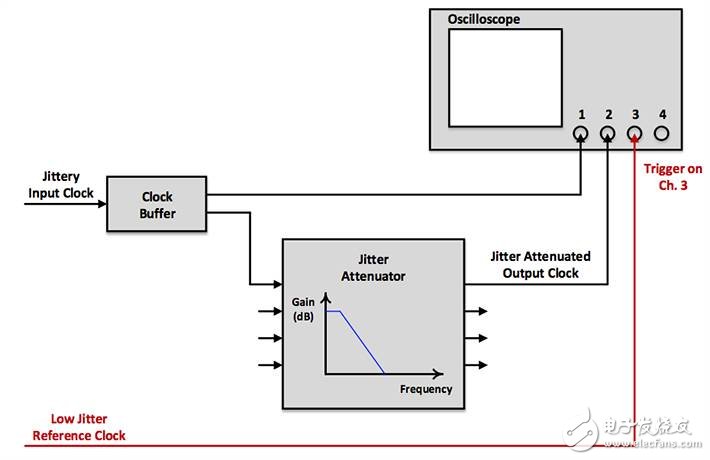

第三方仲裁如果你有一个范围,那么同时比较抖动输入和抖动衰减输出时钟的更好方法是什么?找到仲裁的第三方。换句话说,找到或生成与抖动参考时钟相关的整数,并且与输入和输出时钟同步。然后使用其作为输入和输出时钟的触发的参考。请参见下图中修订的测试设置图。现在,您可以在时域中同时明确比较输入和输出时钟的抖动。

以下是几个示例图,其中所有示波器走线如前所述为25 MHz。顶部的黄色轨迹是抖动(调频)输入时钟,中间的绿色轨迹是抖动衰减器的输出时钟。底部的蓝色轨迹是用作触发的新的低抖动参考时钟。首先,在下图中,抖动衰减器的环路BW为4 kHz,输出时钟像输入时钟一样抖动。

在第二种情况下,在下图中,抖动衰减器的环路BW为100 Hz,输出时钟的抖动要小得多。在这个特定的例子中,当环路BW从4 kHz降低到100 Hz时,抖动衰减时钟周期与周期抖动的标准偏差从8.2 ps下降到1.1 ps。

- 详解:附加相位噪声测试技术及测试过程注意事项(07-08)

- 作为硬件工程师最痛苦你都知道哪些(08-24)

- 高杂波衰减系统关键性能指标介绍(08-27)