教你如何在如何对时钟抖动衰减测试设置

作者:Kevin Smith, Silicon Labs

您好,欢迎来到Timing 101秒懂时钟系列技术文章,本系列文章为Silicon Labs(亦称"芯科科技")时钟技术专家特别开辟的专栏。我们的目标是介绍和综述应用定时组件或IC(也称为"时钟芯片")方面的技术主题。时钟芯片通过时钟波形传送频率和相位信息,并且在某些情况下可以分组化定时信息。

在这篇文章中将介绍一个常见的设置测量的状况,当最初使用抖动衰减器时,其测试结果可能是意想不到的。首先综述一些必要的背景材料,然后展示问题及其根本原因,最后提出改进的测试设置。

抖动和相位噪声简介简而言之,时钟是具有用于在同步数字系统中采样数据的数字信号电平的周期性信号。换句话说,时钟提供了在同步数字电路或系统中采样和顺序处理数据所需的"心跳"或节奏。它们通常但不总是在50%或近50%的占空比。

理想时钟将提供完美的指定频率和相位来优化此过程。然而,实际的时钟具有定时抖动,其可以被定义为时钟边沿与其理想值的短期变化。关心同步数字系统的时钟抖动的一个原因是它可以进入定时裕度,从而影响数据的可靠性和有效性。

还有一个对应于抖动的频域:相位噪声。相位噪声测量时钟的随机短期相位波动。这表明时钟的纯度。

简而言之,这里有一个L(f)的图。显示了在载波频率偏移的情况下,一相调制边带的噪声功率与载波功率的关系。例如,在100kHz时为-70dBc / Hz,在20MHz下为-150dBc / Hz。 dBc / Hz单位是指相对于每赫兹带宽的载波功率的功率(dB)。相位噪声通常使用相位噪声分析仪或具有相位噪声选项的频谱分析仪进行测量。

通常在同一图上显示的是非随机的短期时钟相位波动,称为spurs或spurious。这些spurious,表示为分立组件,单位为dBc。

与其他系统分析一样,我们通常会发现在频域中更容易理解时钟设备和时钟分配网络或时钟树。

抖动衰减器的作用必须使用,或至少从相对噪声大或抖动的时钟开始的工作并不罕见。这些可能出于许多原因。例如,当时钟是:

· 从串行数据流中恢复

· 源自噪声大的IC,如FPGA或噪声大的PC板

· 衍生自TCXO或OCXO,具有良好的漂移规格,否则会出现抖动

· "间隙",意味着为了同步的目的缺少边缘

在这种情况下,我们需要一种特定类型的时钟器件,抖动衰减器或"抖动清除器"来衰减或最小化相位噪声并超出感兴趣的偏移频率。然后将所得到的输出时钟分配到需要改进抖动性能的设备。

抖动衰减器的特征在于它们本质上是具有"低通"抖动传递函数的窄带锁相环(PLL)。这就是这些器件衰减频率大于PLL环路带宽(BW)的抖动分量。现代的抖动衰减器通常具有从0.1Hz到高达1或几kHz的宽范围内的可编程环路BW。

相比之下,另一类时钟芯片,即时钟发生器,是主要用于从低抖动源的时钟乘法的宽带PLL。这些设备通常具有大约100s kHz到1MHz的固定环路带宽。

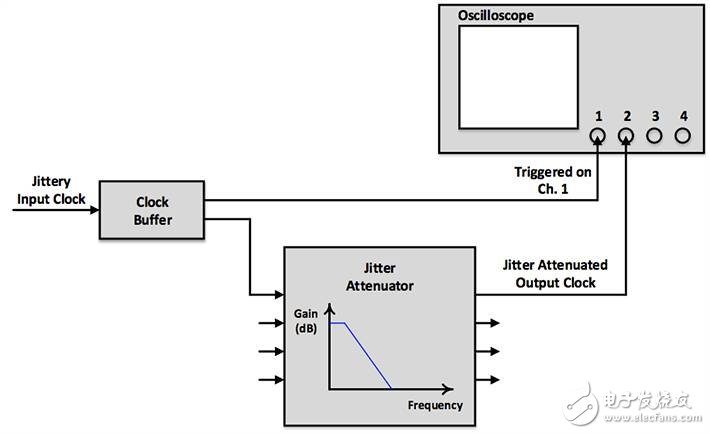

测量的问题那么问题来了?客户经常会和我们联系,并写下像我们正在测试你的一个时钟芯片,并比较输出时钟和输入时钟,但抖动很大。我们总是会发现,测试设置归结为如下所示:示波器被抖动输入时钟触发。

结果通常看起来与下面所示的相似。在这个例子中,抖动衰减器是一个Si5347,其环路BW = 100Hz。顶部的黄色轨迹是输入时钟,该信号是来自信号发生器的25 MHz正弦波,信号发生器采用1 kHz FM,100 Hz偏差。底部的绿色轨迹是输出时钟,只是为了保持简单,也是25 MHz。

输出时钟应该不那么抖动,抖动是否衰减?这是抖动衰减时钟的情况。

考虑到前面所述的测量设置,必须有三个因素来观察这个明显的问题:

1. 输入时钟抖动。

2. 输出时钟抖动不大。换句话说,抖动衰减器正在做它的工作。

3. 输出时钟通过与输入时钟比较由输入时钟触发。

现在您应该能够认识到基本的问题,即使其隐藏在更复杂的应用程序中。

请注意,如果您在输出时钟上触发,那么输入时钟将看起来抖动很大。见下文。哪个时钟出现抖动只是一个触发视角的问题。在不知道哪个时钟更加不稳定的前提下,这种特定的范围测量并不是决定性的。

您可以通过抖动衰减器的环路带宽来获得有关此特定测试配置的真实情况的信息。尝

- 详解:附加相位噪声测试技术及测试过程注意事项(07-08)

- 作为硬件工程师最痛苦你都知道哪些(08-24)

- 高杂波衰减系统关键性能指标介绍(08-27)