在非冗余电源环境中利用LTC4370做一个坚固的负载均分控制器

LTC4370 是一款双电源均流二极管 "合路" 控制器,用 MOSFET 构成理想二极管。以这种方式,LTC4370 可主动地平衡两个电源的输出电流,甚至是那些输出电压不相等的电源。就两个电压不相等的输入电源而言,控制电压较高的电源之二极管正向电压,以平衡均分的负载电流。最大可允许压降由 LTC4370 RANGE 引脚端的一个电阻器设定。

通常情况下,用 LTC4370 均分两个电源的输出电流,当一个电源降至低于 LTC4370 RANGE 引脚设定的共享电压门限时,另一个电源能够提供全部负载电流 (参见配文)。

然而,在非冗余系统中,仍然能够实现使用均流功能的优势,这时两个电源的负载电流之和等于或超过负载所需电流。

在正常运行时,LTC4370 允许电压较高的电源提供全部负载电流,但是在另一个电源不能提供全部电流的情况下,必须防止这样运行。本文介绍了在这种情况发生时,一种停用下游负载的解决方案。

运 行 规 则

在正常运行时,LTC4370 监视两个电源的电流。通常情况下,使用一个完美的二极管时,电压较高的电源会向负载提供全部电流。LTC4370 通过线性地控制电压较高电源的 MOSFET 来防止发生这种情况,以提供与电压较低电源相等的电流。所允许的最大压差由 RANGE 引脚和地之间的电阻器决定。

当输入电源电压之差增大至超出设定范围时,LTC4370 停用均流功能。有两个报警输出,各自监视每个 MOSFET 栅极的控制电压。在正常运行时,如果任一 MOSFET 关断 (表明电压差超出设定范围),与其相关的 FETON 信号就设定为逻辑低。

理论上,看似如果这些信号通过一个逻辑 AND 功能电路,那么就可用来控制下游负载,从而当 MOSFET 关断时 (表明均流失效) 停用下游负载。然而,当通过 MOSFET 的电流为零时,这些信号都返回逻辑低状态。在这种情况下,随着下游负载被停用且不吸取电流,系统会无限期保持这种状态。

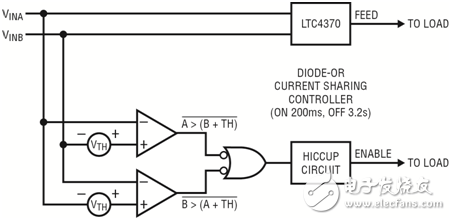

这里介绍的解决方案检测输入电压差,并在检测到设定的电源电压之差时,停用下游负载。这个电压差设定为低于 LTC4370 的最大电压门限。如果检测到失衡情况,那么下游电源就被停用。为了防止发生震荡情况,电路进入打嗝模式,电源每隔 3.2 秒周期性接通 200ms。方框图如图 1 所示。

图 1:电流求和电路的方框图

如方框图所示,两个比较器用于检测什么时候电源输入 VINA 和 VINB 之间差异的绝对值超过了实现正确均流所允许的数值。当发生这种情况时,假真 "或" (OR) 门为逻辑高电平,从而使能打嗝电路。正常情况下,打嗝电路的输出为逻辑高电平,以使能下游负载。当检测到超出范围的故障情况时,打嗝电路被激活,从而引起一个逻辑低电平以停用下游负载。打嗝电路在 200ms 的导通周期里监视电压差动,并在故障情况被清除时停用。

电 路 介 绍

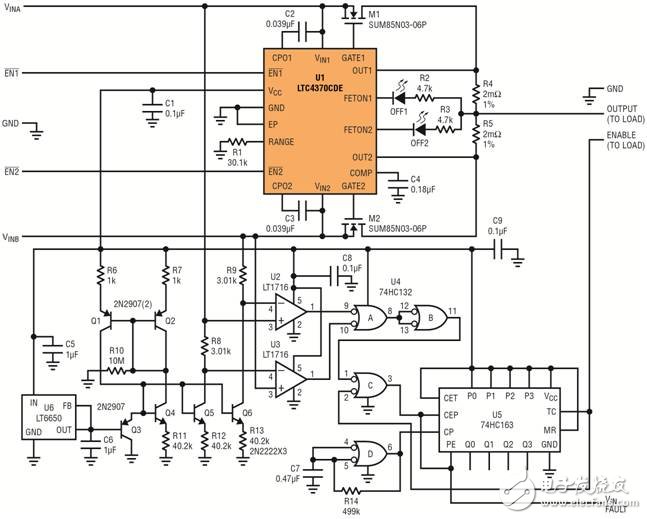

图 2 显示了完整的解决方案。在图 2 中,U2 和 U3 是用来检测 VINA 和 VINB 电压差的 LT1716 Over-The-Top® 电压比较器。

图 2:完整的负载均分设计

比较器的门限偏移电压由电流吸收晶体管 Q5 和 Q6 结合 R8 和 R9 提供。Q5 和 Q6 的集电极电流用晶体管 Q1、Q2、Q3 和 U6 稳定在 100µA,U6 是 LT6650 电压基准。在这种情况下,R8 和 R9 设定为 3.01k,从而产生 300mV 偏移。这些电阻器的值可以更改,以提供不同的偏移,与 LTC4370 的偏移电压相匹配。

当比较器 U2 或 U3 达到该偏移决定的门限时,它们的输出就变成逻辑低,从而启动打嗝电路。

U4 是 74HC132 四通道 CMOS NAND 门控电路,每个输入都具迟滞。U5 是 74HC163 4 位可编程 CMOS 计数器。

当 VINA 和 VINB 在 R8 和 R9 设定的门限以内时,U4A 的输出为逻辑低。当 VINA 和 VINA 超出这一门限时,相应的比较器输出变为逻辑低,导致 U4A 的输出变为逻辑高。

U4A 的一个逻辑高电平输出由 U4B 进行反相,因而在 NOR 门 U4C 的一个输入端上产生一个逻辑低电平。U4C 的合成逻辑高电平输出导致计数器 U5 开始计数。第一个计数为零,致使 TC (终止计数) 引脚变至逻辑低电平。由于从其输出至 NOR 门 U4C 的另一个输入之反馈的原因,该输出在接下来的 15 个计数中保持低电平,这与来自 U11B 的输入无关。在进行第 16 个计数时,TC

- 新颖的均流 IC 可轻松平衡两个电源(11-12)

- 需要用两个电源的电流之和支持负载时,可采用均流控制器(07-11)

- 12V、10A负载均分电路图(09-22)

- 面向高可用性系统的理想二极管和热插拔控制(04-15)