运放中的那些坑——第二篇

ut提供,它会比V1高,另外一份由V2out提供,它会比V2低。

再看原理图,在20mA的时候,Vin+达到了10V,Vin-是5V,放大2倍,在仪放内部需要将Vin+放大到12.5V。这已经超过了仪放供电电压,因此,是绝对不可能正常工作的。

9、运放十坑之九——ADC的采样时间被运放拖累

ADC采集信号,信号稳定的时候,很准确;信号变化的时候,数据不稳定。当然了,ADC有采样时间,软件工程师也知道,他采了10次,只取后5次,但是数据还是有不稳定的状态。让硬件来看电路,硬件工程师说,电路当然没有问题了,全是从别人那里扣来的,怎么在我这就有问题了?

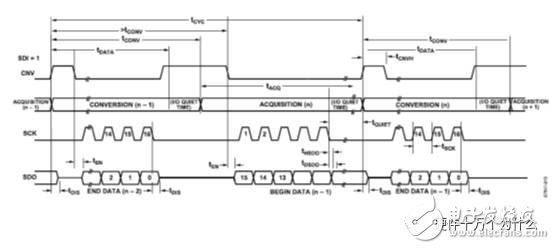

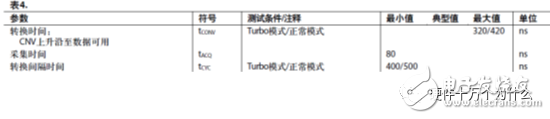

先看ADC的指标Tcycmin=500ns和Tacqmin=80ns,这是颗SAR型ADC,速度能上Mbps,还算挺快的。所以,它连续采样10次,所用时间也才10μs左右。

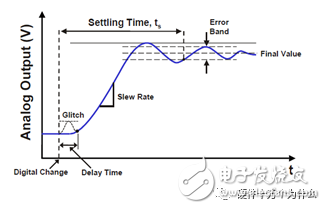

而运放从信号输入到输出,并不是一个无延时的过程,而是一个有延时还带震荡的过程,同时,这个过程的时间还会因为后级线路的PCB设计而增大。如下图:

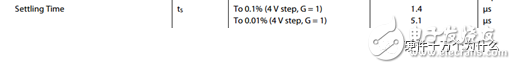

看一下运放的指标,当4V时,达到0.01%,时间为5.1μs,此时带来的波动误差是0.4mV,而在4V范围内,一个16位ADC的1LSB为0.06mV。误差可以吃掉6,7个码字,如果再加上分布电容和走线电阻,这个时间会进一步增加,使得后级稳定时间增长,从而导致误差变得更加的大。

后来,软件工程师调低了采样率,增加了采集时间,问题得以解决。

10、运放十坑之十——被遗忘的功耗

做过一款板卡,功耗要求很严格,因此,设计完成后,就画了电源树,计算了每个器件的功耗,没有超,然后投版,调试,一上电,功耗超标。

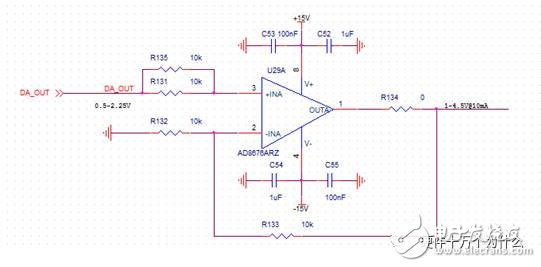

后面一检查,发现是运放功耗计算的时候出现了问题,下图这样的运放电路用了5个。

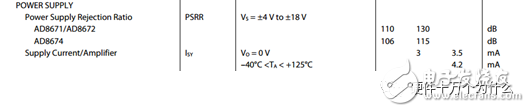

由于是直流驱动,在计算的时候,只考虑了运放本身的静态功耗,PD=15V x 4.2mA =63mW,按照最大静态功耗来考虑,功耗余量还绰绰有余。

实际上,忽略了一个重要的功率消耗点:运放供电电压15V到输出电压(1V-4.5V)之间的电压差,全部在运放里面消耗了,按照最大压差计算,一个电路就消耗140mW。这种耗散功率,以前从来没有考虑过,所以,全部都选择性的忽略了,当遇到功耗要求紧张的需求时,问题就暴露出来了。

后面改版的时候,选择了低电压给运放供电,减少了耗散功耗,满足了指标要求。

运放 相关文章:

- 运放电源过压保护电路设计(06-28)

- 保护运放电源电压极性反接措施及其电路设计(06-28)

- 高压运放可改善性能并缩减电路板空间(08-14)

- 基于 LT6015 / LT6016 / LT6017 的运放精准型正压和负压限幅器(10-07)

- 如何采用面向低噪声的运放进行设计?(04-06)

- 电流源设计小Tips(一):如何选择合适的运放(11-17)