运放中的那些坑——第二篇

6、运放十坑之六——不可忽略的压摆率

做1pps驱动电路,要求上升沿≤5ns,FPGA输出的信号用运放跟随增强驱动后,发现上升沿达不到要求。为什么呢?因为没有考虑到一个重要的指标,压摆率。压摆率是指:输入为阶跃信号时,闭环放大器的输出电压时间变化率的平均值。即输入一个理想的阶跃信号,输出会是一个带斜率信号,这个信号的爬升速率就是压摆率。

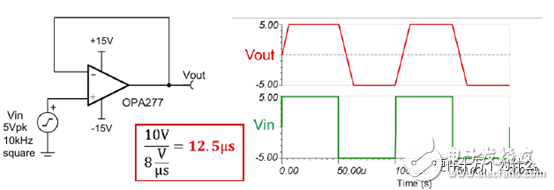

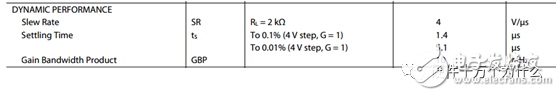

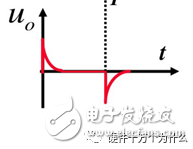

看一下这个运放的压摆率:

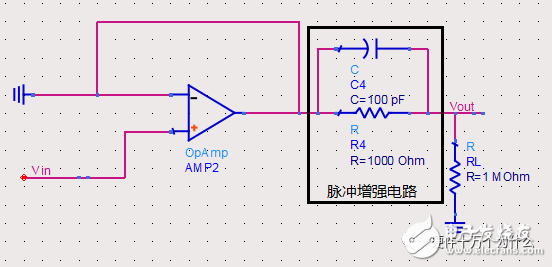

根本达不到要求啊,5ns只能爬升20mV,所以,上升沿根本达不到设计需求。怎么办呢?后期飞线增加了一个脉冲增强电路。

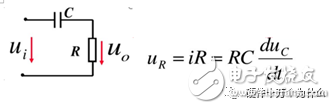

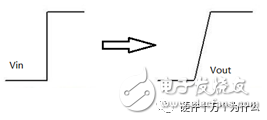

脉冲增强电路C4和R4,相当于一个微分电路C4和RL(当C x RL远小于压摆率时间)加一个直流电阻R4,使得负载RL上的信号边沿变得更加陡峭。分析一下:

a.电容C4与RL形成分压电路,根据下图的计算公式,C4上电压的变化率等于RL上的电压值。

b.那么假设电容电压变化率在0-τ范围内是几乎不变化的,那么负载RL上面的电压也是几乎不变的,一旦电容开始充电(电压发生变化),负载RL的电压就上升到顶点。记为波形1,如下图。

c.然后在电容充电结束后开始下落,为了解决没有变化率就没有电压的问题,增加一个直流电阻R4维持波形,它是一个直通波形,也就是原始波形,记为波形2。

d.两个波形合在一起后,由于波形1,波形2的上升沿得到极大增强,从而使得合成波形上升沿得以改善。

7、运放十坑之七——电流反馈型运放的反馈电阻

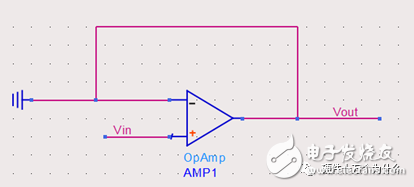

为了扩大外部驱动能力,一般会在最后一级增加一个跟随电路,选择电流反馈运放-CFA增加运放的输出带宽。好简单哦,可惜你就是调不出来。还是先看图吧。好简单哦,可惜你就是调不出来。还是先看图吧。

什么电源轨、共模输入范围、增益积带宽、带载能力、压摆率。。。我全都考虑了啊,还是不对呢?

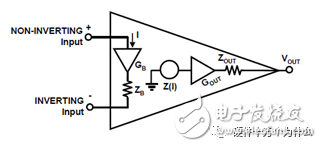

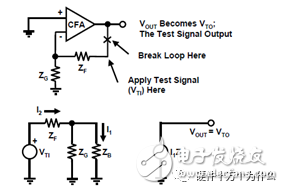

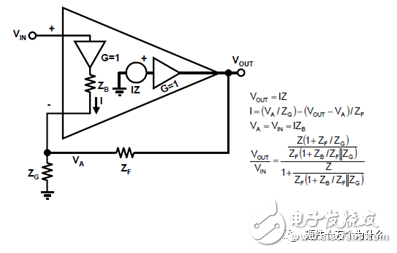

因为,CFA和VFA(电压反馈运放)不一样,读书时学的运放,基本上老师都是拿VFA进行举例和讲解。下图是CFA运放的模型:

它与VFA区别是,输入端不再是两个都虚断,反相输入电阻ZB是个非常小的值,但又绝对不能认为是零;它的开环增益Gout不再是非常大,而是约等于1;它的跨阻Z可以认为是无穷大。

因此,CFA的跟随电路的电路模型如下:

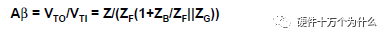

解出Aβ等于:

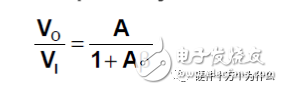

它的闭环增益是:

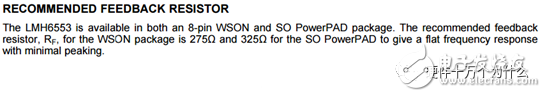

当没有反馈电阻ZF的时候,A约等于1,ZF趋近于0,Aβ趋近于无穷,增益趋近于0,和想要的跟随电路完全不一样,也就是网上常说的"CFA不加反馈电阻就没信号"。(没找到这句话,忘记是在哪里看到的了,只能看下CFA手册上对反馈电阻的介绍)

因此,要增加一个反馈电阻,电路就会正常工作了。

PS:上面推导计算有技巧,只能从Aβ进行计算推导,因为CFA的计算前提是反相输入电阻ZB是个非常小的值;它的跨阻Z可以认为是无穷大,所以,要在求极限是找到一个单一变量,如果按照最终表达进行求极限,一个函数,三个变量(ZF趋近于0,ZB趋近于0,Z趋近于无穷),没法玩,如下图。

8、运放十坑之八——失效的AD620

在我读大学的年代,仪用放大器绝对是一个高X格的词语,在那个还常见三运放搭差分运放的年代,仪放是超高共模抑制比、高温度稳定性的代名词,正相反相两个电压差一减,就得到了结果,这绝对是一个采集EEG信号(脑电波(Electroencephalogram,EEG)是一种使用电生理指标记录大脑活动得方法)的好东西啊。

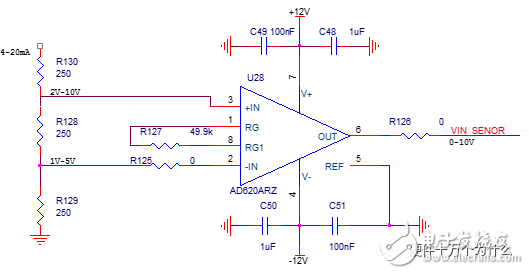

由于EEG信号幅度很小,加上前级放大,也不过1V左右,因此,屡试不爽也没什么问题。后来要做一个工业现场信号检测,就不正常了。还是先看图吧:

采集4-20mA电流,得到1V-5V电压差,放大2倍后进入后级ADC。为了防止电阻功耗过高,R128,R129,R130三个电阻采用了并联取值的方式,最终取到了250Ω这个值。

分析一下,正相输入端2V-10V,符合器件输入范围(VCC-1.4V),反相输入端1V-5V,我加了负电,那更是符合了;然后看放大倍数2倍,Vmax=10V,也符合器件输出范围(VCC-1.4V);电源、放大倍数、去耦等等都没有问题。这是一个显得没有任何错误的原理图,但是实际上,它会在高输入电压值时发生错误。

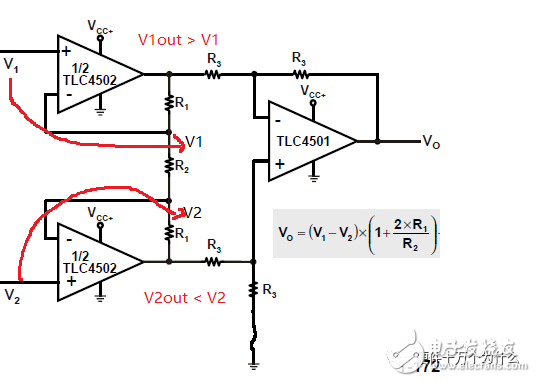

看下仪放的内部原理,就明白了(这里选一个手上有的资料,非AD620的内部原理,其实仪放原理都差不多)

正相输入电压和反相输入电压体现在仪放内部的R2处,而真正进行输出的电压,是由V1out和V2out体现的,换一句话说,最终增加的电压值平分为两份,一份由V1o

运放 相关文章:

- 运放电源过压保护电路设计(06-28)

- 保护运放电源电压极性反接措施及其电路设计(06-28)

- 高压运放可改善性能并缩减电路板空间(08-14)

- 基于 LT6015 / LT6016 / LT6017 的运放精准型正压和负压限幅器(10-07)

- 如何采用面向低噪声的运放进行设计?(04-06)

- 电流源设计小Tips(一):如何选择合适的运放(11-17)