低功率IQ调制器的基带设计实例—电路精选(1)

频谱分析仪以确认实现了期望的调制器 RF 输出频谱纯度。

以较高的 VRMS 驱动 IQ 调制器可提供较高的输出功率,或以较低的 VRMS 进行驱动以实现较低的互调失真 (IMD) 和更好的调制准确度。放大器反馈电阻器可以针对该目的进行调整。

仿真结果

滤波器合成应该已经是正确的。然而,由于滤波器设计必须从单端转换至差分,因此为设计误差的混入提供了一些空档。另一个误差来源可以是放大器中的延迟,对于较高的符号率,它将变成一个因素。快速 LTspice 仿真对于验证这两个误差来源均处于良性状态会有所帮助。

首先,我们分别察看通带和阻带响应:

图 5:总体电路通带响应。这里,我们寻求的是在最高信号频率 (在本例中为 20.25kHz) 下实现最小的增益滚降和群延迟变化。

请注意,20.25kHz 最高信号频率下的响应性能下降仅为 0.5dB。低于 1dB 是一个良好的目标。而且,群延迟如此平坦以至于您将需要采用差值光标在上面的仿真图上测量它。它仅为 3.7ns,与 1/30k (即 33.3µs) 的符号周期相比是可以忽略不计的。小于一个符号周期的百分之几是不错的目标。由于采用了 Bessel 滤波器,因此群延迟变化在该场合中是非常好的。

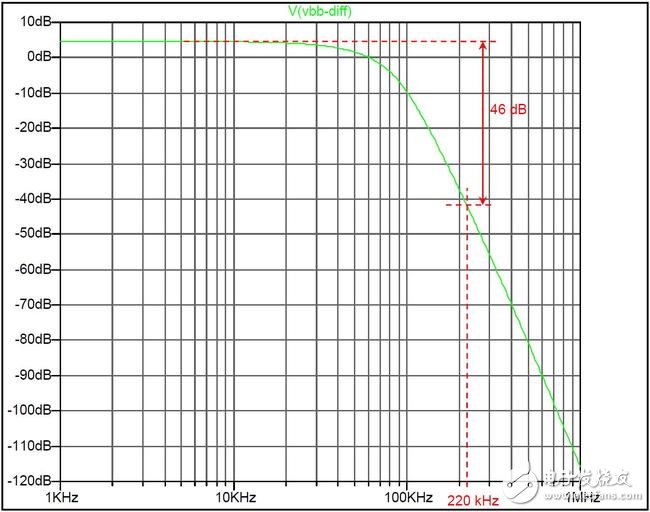

图 6:总体电路阻带响应。这里,我们寻求的是在奈奎斯特镜频 (在该设计实例中为 220kHz) 下实现足够的衰减。

在本例中,我们发现在镜频条件下的衰减为 46dB。与 25dB sin(x) / x 相组合,那就是 71dB。这里,良好的目标是达到约 70dB 或更佳的水平。对于空中传递的应用,监管机构的要求在其中是起作用的。

请注意,滤波器元件损耗会不那么容易准确地仿真。它们的影响在下一个主题中将是很明显的:

测试结果

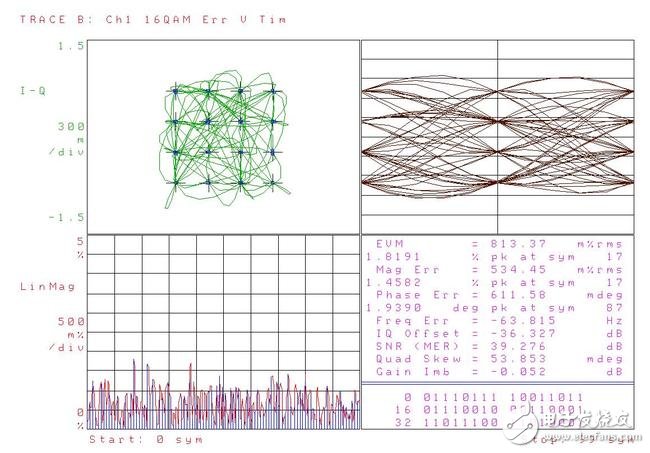

对于数字调制,调制器准确度的终极测试是 EVM。

图 7:LTC5599 0.8% rms 的 EVM 测量结果与预期相吻合。所有的 SPI 寄存器均位于默认值 (被设定在 450MHz 的 LO 频率除外)。

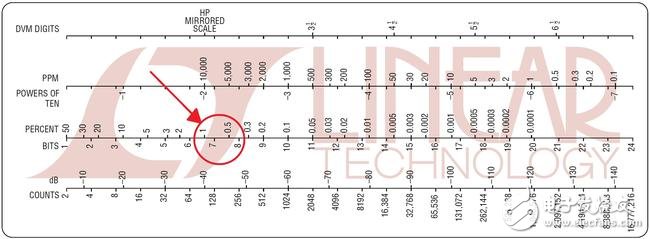

考虑到该系统采用的是 8 位 DAC,因此 EVM 测量值在 0.8% 左右是不足为奇的,因为从根本上说这大概是可获得的最佳结果 (鉴于有效位数 [ENOB] 将小于 8 位):

图 8:要求提供免费的凌力尔特准确度转换器!在该场合中,它说明了 DAC 有效分辨率会怎样限制调制准确度。

EVM 测试结果与先前公布的测量结果相吻合,而且对于大多数数字调制应用来说肯定是足够好了。

进一步的 EVM 改善将需要更多的 FIR 滤波器抽头、更高分辨率的 DAC、也许还包括某种针对 sin(x) / x 滚降和 DAC 重构滤波器滚降的数字滤波器补偿。

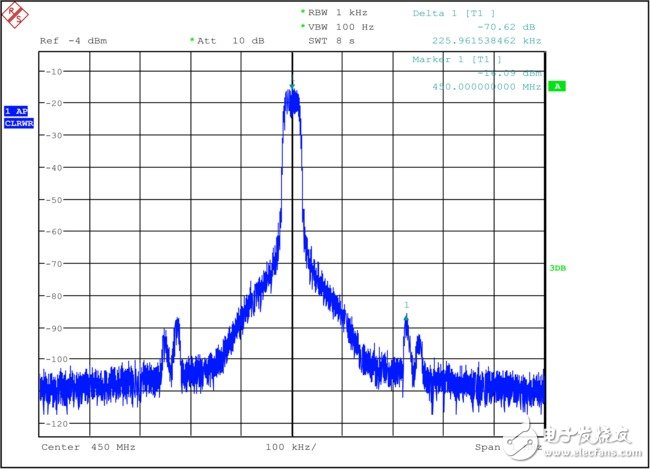

图 9:在 -4dBm 输出功率下的 RF 输出频谱。请注意,最差 DAC 镜频抑制度约为 -70dBc,对于大多数应用而言足够好了。

察看一下输出频谱,接近噪声频谱密度由若干因素决定:FIR 滤波器阶数、LO 相位噪声和调制器驱动电平。

编者结论

本篇文章举例说明了针对利用 LTC5599 和 LTC5589 等低功率 IQ 调制器的详细设计方法。如在这里用实例介绍的那样,为了获得最高的调制准确度、最低的噪声和最低的 DC 功耗,设计师必须谨慎地考虑每个电路功能块。

- 通讯系统架构详解:基带、中频、射频零部件(09-17)

- 基于DSP的数字对讲机基带系统中的应用(05-06)

- 卫星导航系统基带伪码完整系统解决方案(08-06)

- 高效地SDR基带处理——车载智能触摸屏必不可少的一步(07-31)

- 利用软件无线电(SDR)实现基带信号处理方法(08-16)

- 方便工程师更灵活更方便设计电源的解决方案(04-10)