数字电路之时序电路

时间:07-02

来源:网络

点击:

关于时钟同步电路的注意事项。

在「组合电路」中,微小的信号传输迟延,都有可能造成输出毛刺。尽管毛刺是一个极其短暂的信号,但也可以引起逻辑电路的误动作。为了回避这个问题,就要使用时钟同步电路。

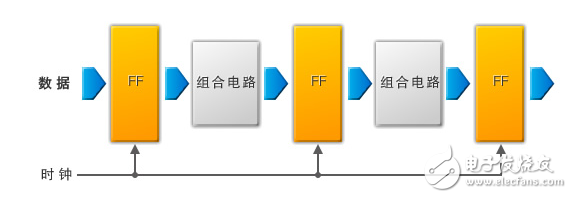

图10:时钟同步电路的思路

图10给出了时钟同步电路的概要。如图所示,其构造是在FF(触发器)之间夹着「组合电路」。毛刺是「组合电路」在输出稳定之前,输出的短暂信号。因此,在「组合电路」输出稳定以后,再改变时钟,用触发器保持这个输出,就可以回避这种误动作了。

至此,数字电路入门的三次讲座全部结束了。从「什么是数字?」开始,逐步讲解了「基本逻辑电路」、「数字IC的基础」、「组合电路」和「时序电路」。 实际上,电路设计方面还有很多很多必须学习的内容。请大家一定要自己找时间继续学习!

- 新一代LED光耦电路设计,改进老化和能耗(10-05)

- Eyeronman震动马甲:让盲人通过触觉“看”到世界(10-19)

- 基于555流水灯电路的设计与实现(02-25)

- 施密特触发器与电阻式传感器之间的绝密关系(10-05)

- RS触发器工作原理_RS触发器逻辑功能_RS触发器和SR触发器的区别(07-09)

- 基于集成电路CD4013的双稳态电路(07-04)