FPGA数据采集电子电路设计攻略

时间:04-15

来源:网站整理

点击:

编帧和解帧

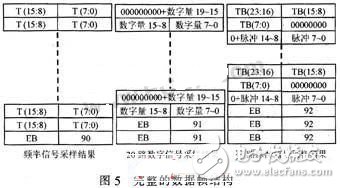

在数据采集部分中,当同步信号的上升沿到来时,将3个帧标志分别写入3个缓存,频率信号数据的帧标志为EB90;20路数字信号的帧标志为 2个EB91;15路脉冲信号数据的帧标志为3个EB92。读取数据模块中,当同步信号的下降沿到来时,开始读取缓存的数据送至外部FIFO,并判断当读取一个EB90后,开始读取缓存的数据,并送入外部FIFO;当读到两个EB91后,读取缓存的数据,并送入外部FIFO;当读到3个EB92后表明一帧数据读取完毕,等待下一个同步信号的下降沿后再开始读取下一帧数据。由于外部FIFO是16位,所以数据中不满16位的都用0将数据补充完整,完整的数据帧结构如图5所示。

上位机收到一帧数据后进行解帧处理,对于频率信号数据,将这些T值相加并求平均得出T’,再乘以2,由于系统时钟是120 MHz,所以2T’/120为频率信号周期(μs级),然后求倒数即可得出该信号的频率值。20路数字量信号数据直接显示其电平状态。脉冲信号数据则先判断哪一路(多路)脉冲信号发生变化,再判断该信号(几路信号)的电平状态。若为高电平,则对应的时间应为TBa;若为低电平,则对应的时间应为TBb。TBa即为该脉冲信号相对于同步信号的延迟,而TBb-TBa的值即为该脉冲信号的正脉冲脉宽。

- 盘点:那些为健康而生的APP与智能硬件(11-24)

- 指尖的密码!手指静脉识别鼠标问世(02-02)

- WLAN射频优化的解决方案设计详解(03-03)

- 智能鞋垫:解决跑步者的膝伤问题(02-12)

- 混合动力汽车系统结构大盘点TOP3(03-14)

- 盘点STM32-NUCLEO开发与仿真平台(03-28)