FPGA电子电路设计图集锦TOP12

,来完成两者的通信。计算机通过应用程序、动态链接库的有效配合将控制命令信号发送到FT245BM,FPGA 利用与之相连的I/O 口接收下发的控制命令或是发送上传的测试数据。

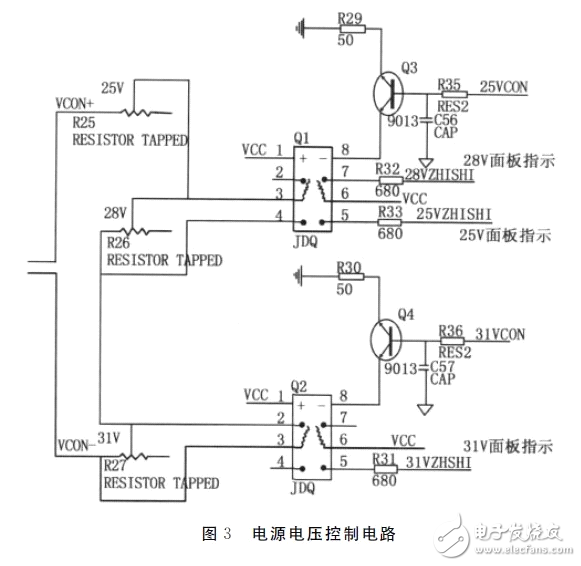

输出电源电压控制模块实现

由于需要为被测数字量变换器提供3档工作电压25V、28V、31V,在电源模块输出端连接三种不同阻值的电阻,就可以实现3种电压的切换,实现控制的电路如图3所示。

图中VCON+,VCON-为电源模块的输入电压,R25、R26、R27三组电位器用来调节电阻。25VCON、31VCON 分别与FPGA 的I/O 相连,是FPGA 给出的控制信号,电路中三极管的作用是利用其电流放大来增加信号的驱动能力。通过FPGA 对控制命令的判断来实现3档电压的控制。此外,系统的默认及复位的输出电压为28V。

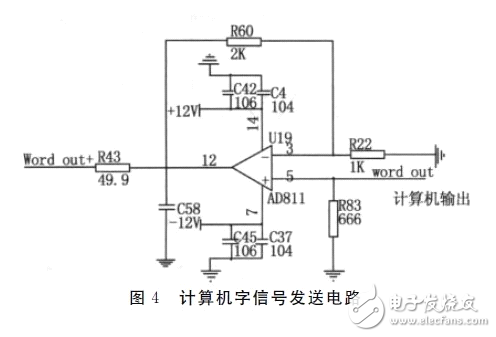

计算机字信号发送模块实现

由于要求计算机字和移位脉冲的幅值都为8~10V,所以电路中采用运算放大器电路对FPGA 输出的信号进行放大来获取所需幅值的信号。计算机字信号发送电路如图4所示。

为了满足输出信号的精度和电流驱动能力的要求,本模块中采用AD 公司的运放AD811来设计电路。此运算放大器是高速运放,采用双电源供电,2500V/us 是其最高转换速率,具有较低的电流、电亚噪声。设计中采用同相放大电压串联型负反馈电路,输出电压稳定并且反馈效果好。电路中R83的接地是为了尽量减小由于偏置电流引起的电压失调,其阻值等于R22和R60的并联阻值,为R22//R60=666Ω。

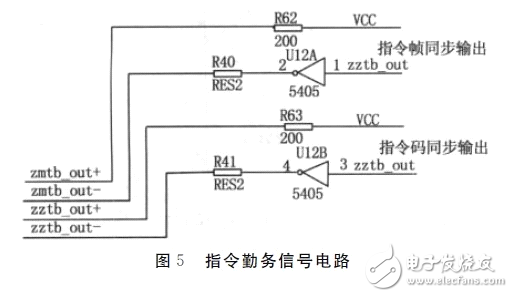

TOP6 勤务信号发送模块实现

计算机字信号和指令信号都有相应的勤务信号来满足时序要求,一般勤务信号就是指帧、码同步信号,对其他信号的产生和接收起到时序基准同步的作用。指令勤务信号的电路原理如图5所示。计算机字勤务信号与其原理相同。根据系统的信号输出要求,即帧、码同步信号的幅值和电流驱动能力的要求,采用非门芯片 SN5405J 作为驱动电路来满足设计要求。

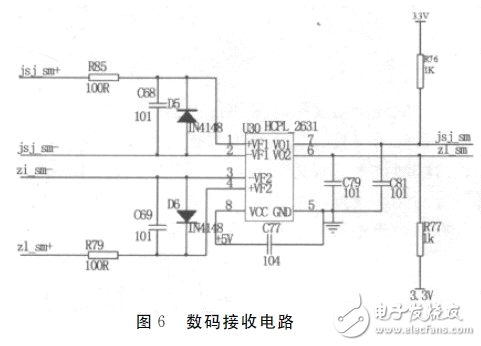

数码接收模块实现测试系统需要接收经变换器处理之后的信号,变换器以数码方式回传给测试系统,包括计算机数码和指令数码,两者的接收原理相同。设计采用光耦隔离的方式对数码信号进行接收,其电路原理图如图6所示。

光电耦合器采用TI 公司的HCPL-2631,它具有电绝缘能力和抗干扰能力,并且能有效的抑制各种噪声和尖峰脉冲干扰。它的两个输入端分别接收计算机字数码和指令数码,其中在光耦输入端连接的二极管作用是用来防止信号反跳造成内部二极管烧坏。

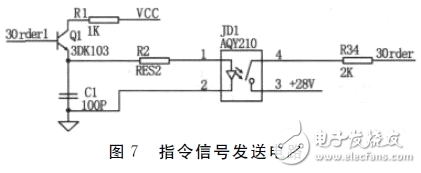

指令信号发送模块实现

指令信号是指一种断开或闭合的开关量信号。此模块的128路指令信号全部采用光耦继电器来实现,依据参数要求选择AQY210作为控制开关的器件,它的特点是耐高压,反应速度快,使用时间长。其单路指令信号发送电路原理如图7所示。

由由于指令信号的路数比较多,如果FPGA 的I/O 口输出直接驱动AQY210,势必会增加FPGA 的功耗。因此采用三极管对FPGA 的输出信号进行电流放大来提高控制信号的驱动能力。本设计采用NPN 型三极管3DK103,图中3order1是FPGA 的输出信号,其为‘0’时,三极管截止;其为‘1’时,三极管处于电流放大,流经光继电器发光管的电流13mA 足以使AQY210导通。

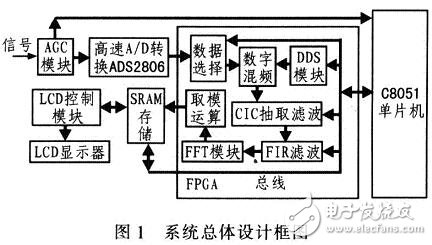

设计方案

图1为系统设计总体框图。该系统采用C8051系列单片机中的 C8051F121作为控制器,CvcloneⅢ系列EP3C40F484C8型FPGA为数字信号算法处理单元。系统设计遵循抽样定理,在时域内截取一段适当长度信号,对其信号抽样量化,按照具体的步骤求取信号的频谱,并在LCD上显示信号的频谱,同时提供友好的人机会话功能。该系统最小分辨率为1 Hz,可分析带宽为0~5 MHz的各种信号。

TOP7 采用FPGA频谱分析仪系统电路

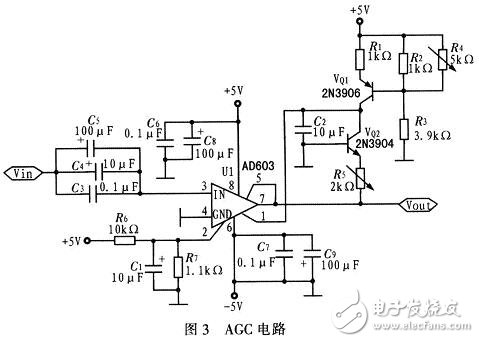

AGC电路

输入信号经高速A/D采样,信号幅度必须满足A/D的采样范围,最高为2-3V,因此该系统设计应加AGC电路。AGC电路采用AD603型线性增益放大器。图3为AGC电路。

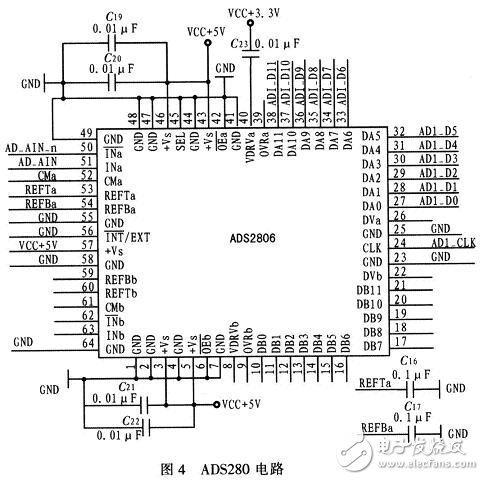

A/D转换电路

ADS2806是一款12位A/D转换器,其特点为:无杂散信号动态范围(SFDR)为73 dB;信噪比(SNR)为66 dB;具有内部和外部参考时钟;采样速率为32 MS/s。图4为ADS2806的电路。为使A/D转换更稳定,在A/D转换器的电源引脚上增加滤波电容,抑制电源噪声。该电路结构简单,在时钟CLK的驱动下,数据端口实时输出数据,供FPGA读取。

FPGA及外围接口模块

选用CycloneⅢ系列 EP3C40F484型FPGA,该器件内部有39 600个LE资源,有1 134 000 bit的存储器,同时还有126个乘法器和4个PLL锁相环。由于该器件内部有大量资源,因而可满足其内部实现数字混频、数

- 盘点:那些为健康而生的APP与智能硬件(11-24)

- 指尖的密码!手指静脉识别鼠标问世(02-02)

- WLAN射频优化的解决方案设计详解(03-03)

- 智能鞋垫:解决跑步者的膝伤问题(02-12)

- 混合动力汽车系统结构大盘点TOP3(03-14)

- 盘点STM32-NUCLEO开发与仿真平台(03-28)