语音识别电路设计图集锦

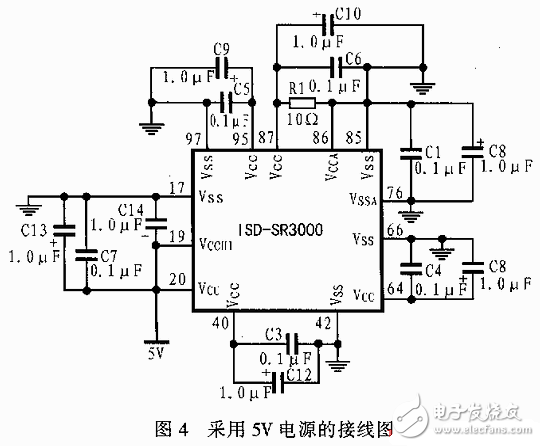

外接晶振可通过X1和X2/CLKIN端与芯片内的振荡电路相连。为减少寄生电容和电感对振荡频率的影响,外接的晶振和电容应尽量靠近X1和X2 /CLKIN端。ISD-SR3000可工作在3.3V±10%和5V±10%两种电压,不同电压的接线方式不同。图3是采用3.3V电源时的接线图,图 4为采用5V电源时的接线图。SD-SR3000具有低功耗模式,在低功耗模式时的电流消耗仅12mA,此时芯片中的一些功能模块处于未激活状态,因而不能进行语音识别。低功耗模式时的引脚CS0和CS1必须置1,这时,MWCLK、MWDIN信号将保持在Vss+0.5V,而RESET、MWCS信号则将保持在Vcc- 0.5V。

TOP6 揭秘DSP和HMM的语音识别系统电路

存储器接口

ISD-SR3000利用扩展的Flash(闪存)和RO来存储声音标签、词汇、提示符和音质模型。建议选用16M以上存储容量的扩展Flash存储器,如Am29LA160D等。外接64kB的SRAM可实现HMM算法。表2给出了扩展地址线的接口信号。

ISD-SR3000可为模拟和数字电话提供一个支持主和从CODEC接口模式的CODEC接口,该接口具有8位和16位的信道宽度,能支持可变和固定格式的通信协议。在主模式下,可利用SR3000来控制CODEC的运行以满足模拟电话和独立标准的应用;在从模式下,CODEC接口由外接信号控制,此模式可用于数字电话,如ISDN或DECT线等。CODEC接口使用的5个信号分别为CDIN、CODUT、CCLK、CFS0和CSF1。其中 CDIN、CDOUT、CCLK和CFS0被连接到第一个CODEC。CDIN、CDOUT、CCLK和CFS1被连接到第二个CODEC接口。数据通过 CDOUT输出端传送给CODEC接口,并通过CDIN输入端从CODEC读出。CCLK和CFS0端在主模式下为输出状态,而在从模式下为输入状态。 CFS1是一个输出端。

揭秘DSP和HMM的语音识别系统电路模块设计

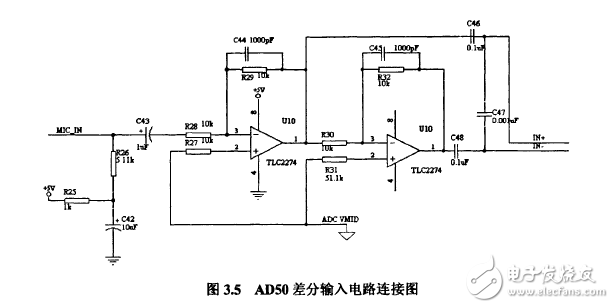

语音信号采集模块主要包括语音信号的输入输出模拟通道、DSP和AD50的连接、DSP和AD50的周边设备连接等。其中,DSP和AD50的周边设备连接包括电源电路、时钟电路、复位电路、存储器扩展电路和去耦电路等,这些电路的连接可查看相关芯片资料。语音信号的前后端处理主要由输入输出模拟通道组成。这两个电路的主要作用是将信号进行处理,尽量减少输入输出引入的噪声。同时,还可以调整输入输出的放大系数,使语音信号适合各种不同的功放,得到最佳的语音效果。为了达到更好的效果,AD50的模拟信号输入采用差分输入方式,即使用两个运算放大器,将单端输入信号转换成差分输入信号,电路连接如图3.5所示。使用差分信号,信号一J下一负同时进入采集系统,如果此时有随机噪声出现,通过『F负信号的加减,可以有效消除部分噪声。

AD50差分输入电路

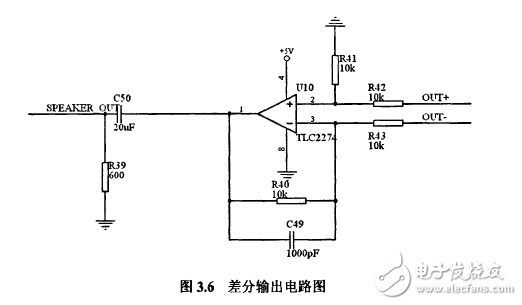

AD50的D/A输出为差分信号,可以直接驱动600欧姆的负载。

差分输出电路

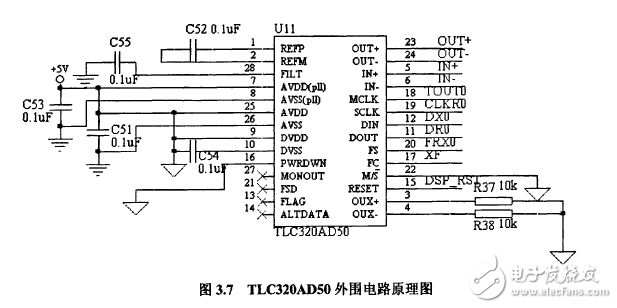

要使TLC320AD50正常工作,还需要进行电源供电及去耦电路以及一些功能引脚包括帧同步延迟输出、电压下拉、输出监控、参考电压过滤输出等的连接,具体连接如图3.7所示。

TLC320AD50外围电路

DSP通过多通道缓冲串口连接AD50。DSP最多可以使一个缓冲串口与3个AD50芯片连接。本系统采用DSP为主设备、AD50为从设备的连接方法。如图3.8所示,AD50的时钟信号MCLK由DSP的定时器0的输出TOUT0提供,时钟频率可以通过设置定时器0来改变。AD50的移位时钟输出 SCLK连接到DSP的缓冲串口0的接收时钟引脚CLKR0,帧同步信号FS连接到DSP缓冲串口0的FRXO。AD50的FC引脚连接到DSP的通用 I/O引脚XF,用于控制二次串行通信。图3.8中DSP的DR0为输入,其余均为输出。

TOP7 程序存储器电路

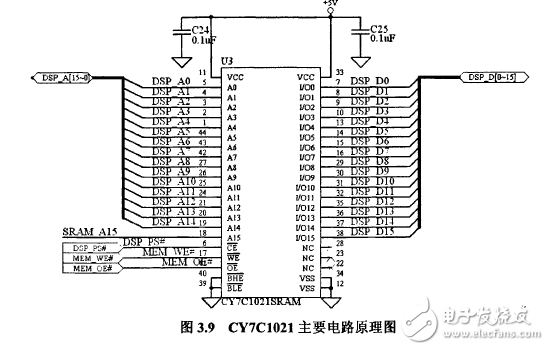

程序存储器主要用于系统运行时,将采集的数字语音信号暂时存储在RAM中以备后续的处理。由于采集的数据不是太大,扩展32k的程序存储器即可满足要求。因此本系统只用到CY7C1021的低32k字空间,将DSP的地址线的低15位与CY7C1021的地址线引脚相连,而地址线的1卜18位通过一个数字逻辑电路后用于寻址CY7C1021的低32k字空间。电路原理图如图3.9所示。

Y7C1021主要电路原理图

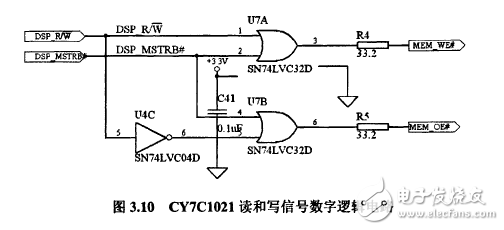

图3.10是CY7C1021读和写信号数字逻辑电路。图中,DSP的DSP—R/W和DSP—MSTRB引脚通过或门后的输出作为SRAM的写信号,DSP—R/W的非和DSP—MSTRB引脚通过或门后输出作为SRAM的读信号。

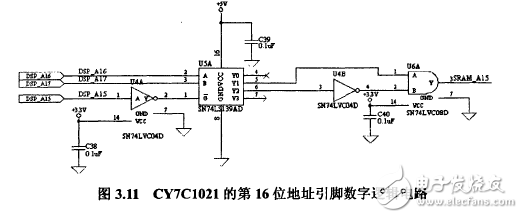

图3.1l是CY7C1021的第16位地址引脚数字逻辑电路。图中,DSP A15经过一个非门作为二四译码器SN74LSl39AD的使能信号,DSP A16和DSP A17经过译码器后输出端Yl与Y2的非通过一个与门后的输出作为SRAM的第16位地址线。因此,低32k的SRAM映射到DSP程序空间的0X1 8000__oXlFFFF。

- 盘点:那些为健康而生的APP与智能硬件(11-24)

- 指尖的密码!手指静脉识别鼠标问世(02-02)

- WLAN射频优化的解决方案设计详解(03-03)

- 智能鞋垫:解决跑步者的膝伤问题(02-12)

- 混合动力汽车系统结构大盘点TOP3(03-14)

- 盘点STM32-NUCLEO开发与仿真平台(03-28)