功率因数校正最佳策略:如何选取合适的MOSFET?

时间:06-25

来源:Vishay公司

点击:

耗有可能在总损耗中占相当大的比例。高压MOSFET (HVM)的Coss随着所施加的VDS的不同而有相当大的变化。为说明输出电容器的非线性,可以使用Poss = ½ Coer x V2 x Fsw作为损耗计算公式。Coer是由产品说明书提供的有效电容,与MOSFET的集成Coss具有相同的存储能量和相同的损耗。所以,新FOM现在为Rds(on)(典型值) * (Qswitch (典型值) + Qoss),其中Qswitch是Qgd和Qgs的组合。

例如,我们使用一个最大封装功率损耗为8 W且对传导损耗和开关损耗的贡献各为4 W的TO-220 / TO-220F器件。这样Coss/Qoss损耗将占到总封装损耗的约20%,或总开关损耗的约40%,这是标准FOM公式没有加以考虑的一个较大损耗。

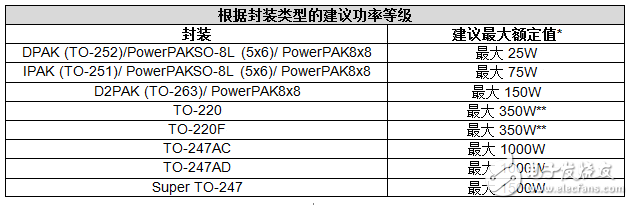

由于有许多可用封装选项,所以表1列出了针对不同封装的最大功率额定值。请注意,每种封装都有一系列器件可供选用,所以有可能对广泛的输出功率推荐相同的封装。为了实现SMT封装(如PowerPAK®SO-8L (5x6) 和PowerPAK®8x8)的最大可能功率耗散,有必要将PCB温度保持在最坏条件下的应用要求值。建议最大额定值因此受到系统热考虑事项而非封装损耗的限制。

表1:各封装类型下的最大功率级

本文选自电子发烧友网6月《智能工业特刊》Change The World栏目,转载请注明出处!

- 基于风力发电系统的电能变换装置研究(10-13)

- 基于PIC16C72的电力三相不对负载无功补偿算法的实现(10-23)

- 无功补偿技术对低压电网功率因数的影响 (05-02)

- 现代逆变器系统的结构功能及其对功率因数校正(06-25)

- 功率因数校正在离线式电源中的应用(07-17)

- UPS标准中功率因数的概念(09-24)