基于USB及EDA的硬件加密系统

时间:07-08

来源:互联网

点击:

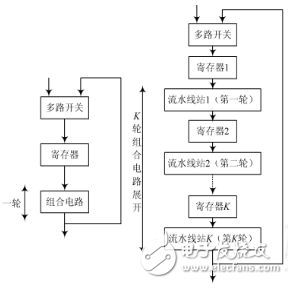

构中,与K轮加密对应的组合逻辑被均分为K个部分,并在各个部分之间添加一个额外的寄存器,其余部件与基本结构相同。这些分割得到的组合逻辑电路部分称为流水线站,每个流水线站执行不同的处理步骤。用这种方法,电路可以同时处理多个数据块,提高系统在单位时间内处理的的数据量,也就是速度。

在每一个时钟周期,被部分处理过的数据块移人下一个流水线站,后续块则紧跟其上,占据他原来的位置,也就是说,一个流水线电路可以同时加密与他所含有的流水线站数量相等的数据块。以这种将循环展开为流水线的处理方式,展开后的流水线处理周期在理想情况下接近于基本结构处理周期时间的1/K。

本文实现的DES算法数据流通路简单,大部分都是针对位的线性变换;算法的核心部分是16轮的完全相同的线性变换迭代,因此可以循环展开为16级深度的流水线;在非反馈模式应用时,前后数据块之间没有相关性,因而不会产生冲突;每一轮运算中需要的子密钥可以提前生成,随数据流在流水线的前进中提供给各级流水线。

4 结语

采用USB 总线技术与EDA技术相结合的设计思路,使系统设计更灵活,系统升级更容易。实现了软件平台的通用化、软件协议的标准化、硬件结构的统一化,从而保证了系统的可移植性和可扩展性,为硬件加密系统的设计提供了一种新思路。加密系统实际运行情况表明,系统设计思路正确,系统实时性、加密性能都能达到设计要求。

- 探索性数据分析(EDA)及其应用(10-18)

- 霍尼韦尔“互联网+医疗”解决方案亮相2016中华医院信息网络大会(04-27)

- 基于EDA或FPGA的IP保护的实现(09-16)

- 基于MC8051 IP核和FPGA的频率计设计(11-24)

- FPGA设计新需求走热 EDA战况升温(03-17)

- 2016年EDA/IC设计频道应用文章精选(02-26)