时序分析中的一些基本概念

定不变的时间。输入信号应提前时钟上升沿(如上升沿有效)T 时间到达芯片,这个T 就是建立时间Setup time。简而言之,时钟边沿触发前,要求数据必须存在一段时间,这就是器件需要的建立时间。如不满足setup time,这个数据就不能被这一时钟打入触发器,只有在下一个时钟上升沿,数据才能被打入触发器。

保持时间(hold time)是指触发器的时钟信号上升沿到来以后,数据稳定不变的时间。简而言之,时钟边沿触发后,数据也必须保持一段时间,以便能够稳定读取,这就是器件需要的保持时间。如果hold time 不够,数据同样不能被打入触发器。

如果不满足建立和保持时间的话,那么DFF(D type flip-flop/D类型触发器) 将不能正确地采样到数据,将会出现亚稳态(metastability )的情况。如果数据信号在时钟沿触发前后持续的时间均超过建立和保持时间,那么超过量就分别被称为建立时间裕量和保持时间裕量。

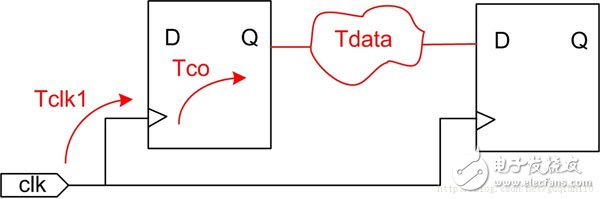

7. Data Arrival Time

输入数据在有效时钟沿后到达所需要的时间。主要分为三部分:时钟到达寄存器时间(Tclk1),寄存器输出延时(Tco)和数据传输延时(Tdata)

Data Arrival Time = Launch edge + Tclk1 +Tco + Tdata

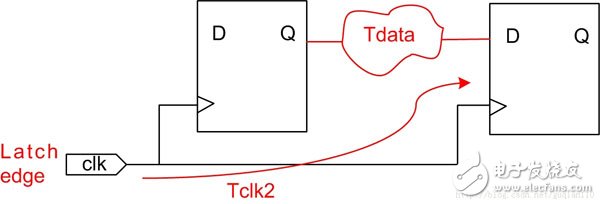

8. Clock Arrival Time

时钟从latch边沿到达锁存寄存器时钟输入端所消耗的时间为时钟到达时间。

Clock Arrival Time = Lacth edge + Tclk2

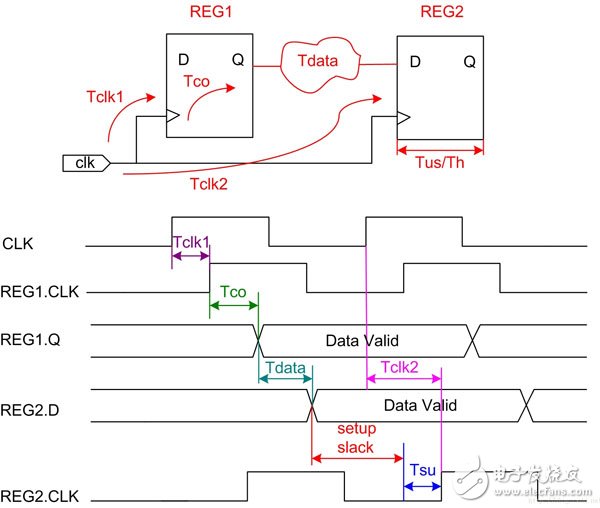

9. 建立裕量 Setup Slack

当数据需求时间大于数据到达时间时,就说时间有余量,Slack是表示设计是否满足时序的一个称谓。

Setup slack = Data Required Time - Data Arrival Time

正的slack表示数据需求时间大于数据到达时间,满足时序(时序的余量),负的slack表示数据需求时间小于数据到达时间,不满足时序(时序的欠缺量)。

10. Recovery/Removal Time

Recovery time is the minimum length of time an asynchronous control signal, for example, and preset, must be stable before the next active clock edge. The recovery slack time calculation is similar to the clock setup slack time calculation, but it applies asynchronous control signals.

Removal time is the minimum length of time an asynchronous control signal must be stable after the active clock edge. The TimeQuest analyzer removal time slack calculation is similar to the clock hold slack calculation, but it applies asynchronous control signals.

recovery time specifies the time the inactive edge of the asynchronous signal has to arrive before the closing edge of the clock.

Removal time specifies the length of time the active phase of the asynchronous signal has to be held after the closing edge of the clock.

也就是说Recovery / Removal time类似于Setup / Hold Time,不过是用于异步信号,比如set,reset信号。他们检查异步型号的边沿,释放沿必须在时钟沿前面提前recovery time释放,或者在时钟沿后removal time之后释放。注意异步复位亚稳态问题!

11. 最大时钟频率

时钟最小周期:系统时钟能运行的最高频率。

1. 当数据需求时间大于数据到达时间时,时钟具有余量;

2. 当数据需求时间小于数据到达时间时,不满足时序要求,寄存器经历亚稳态或者不能正确获得数据;

3. 当数据需求时间等于数据到达时间时,这是最小时钟运行频率,刚好满足时序。

最小时钟周期为数据到达时间等于数据需求时间。

12. 时序分析

分析第9节的图,数据传播的路径从上一级触发器到下一级触发器建立经过的数据时延总和为:Tclk1 + Tco + Tdata + Tsetup-slack + Tsu

在两级寄存器之间,时钟间隔为:Tclk + Tclk2

根据建立时间要求(在下一个时钟上升沿到来的时候,数据必须稳定,且保持一定的时间Tsu)可以列一个不等式:数据时延 < 时钟间隔,即

Tclk1 + Tco + Tdata + Tsetup-slack + Tsu <= Tclk + Tclk2

同理,根据保持时间要求(时钟上升沿到来后,寄存器锁存数据的时候,数据要保持一定的稳定时间Th)可以列一个不等式:

Tco + Tdata <= Th

随着系统时钟 fclk 变大时,Tclk变小,则要求 Tco + Tdata 也变小,当 Tco + Tdata 不满足第一个不等式时,不满足建立时间要求;但是,Tco + Tdata 也不是越小越好,当其太小时,不满足第二个不等式时,触发器不能正常锁存数据,即不满足保持时间要求。从

- SOC时序分析中的跳变点(08-15)

- 在进行时序分析时为什么CPR操作得出的效果却是相反的?(02-07)

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)