FPGA实战开发技巧(10)

5.5.3 SPI串行Flash配置模式

1.SPI串行配置介绍

串行Flash的特点是占用管脚比较少,作为系统的数据存贮非常合适,一般都是采用串行外设接口(SPI 总线接口)。Flash 存贮器与EEPROM根本不同的特征就是EEPROM可以按字节进行数据的改写,而Flash只能先擦除一个区间,然后改写其内容。一般情况下,这个擦除区间叫做扇区(Sector),也有部分厂家引入了页面(Page) 的概念。选择Flash产品时,最小擦除区间是比较重要的指标。在写入Flash时,如果写入的数据不能正好是一个最小擦除区间的尺寸,就需要把整个区间的数据全部保存另外一个存贮空间,擦除这个空间,然后才能重新对这个区间改写。大多数Flash工艺更容易实现较大的擦除区间,因此较小擦除区间的Flash 其价格一般会稍贵一些。此外,SPI是标准的4线同步串行双向总线,提供控制器和外设之间的串行通信数据链路,广泛应用于嵌入式设备中。

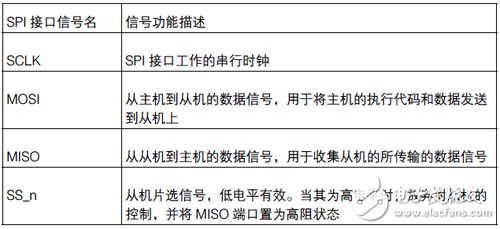

赛灵思公司的新款FPGA都支持SPI接口。SPI总线通过4根信号线来完成主、从之间的通信,典型的SPI系统中常包含一个主设备以及至少一个从设备,在FPGA应用场合中,FPGA芯片为主设备,SPI 串行FLASH为从设备。4个SPI接口信号的名称和功能如表5-2所示。

表5-2 SPI接口信号列表

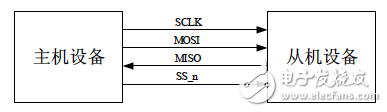

一个主芯片和一个从芯片的通信接口如图5-24所示。FPGA通过SCLK控制双方通信的时序,在SS_n为低时,FPGA通过MOSI 信号线将数据传送到FLASH,在同一个时钟周期中,FLASH通过SOMI将数据传输到FPGA芯片。无论主、从设备,数据都是在时钟电平跳转时输出,并在下一个相反的电平跳转沿,送入另外一个芯片。

图5-24 SPI接口连接示意图

其中SCLK信号支持不同的速率,一般常采用20MHz。通过SPI 接口中的CPOL和CPHA这两个比特定义了4种通信时序。其中,CPOL信号定义了SCLK的空闲状态,当CPOL为低时,SCLK的低电平为空闲状态,否则其空闲状态为高电平;CPHA定义了数据有效的上升沿位置,当其为低时,数据在第1 个电平跳转沿有效,否则数据在第2个电平跳转沿有效。其相应的时序逻辑如图5-25所示。

图5-27 CPHA为低时SPI的总线时序示意图

图5-28 CPHA为高时SPI的总线时序示意图

可以通过增加片选信号SS_n的位宽来支持多个从设备,SS_n的位宽等于从设备的个数。对于某时刻被选中的从设备和主设备而言,其读写时序逻辑和图5-29一样。

图5-29 多个从芯片的连接电路图

SPI串行FLASH作为一种新兴的高性能非易失性存储器,其有效读写次数高达百万次,不仅引脚数量少、封装小、容量大,可以节约电路板空间,还能够降低功耗和噪声。从功能上看,可以用于代码存储以及大容量的数据和语音存储,对于以读为主,仅有少量擦写和写入时间的应用来说,支持分区( 多页) 擦除和页写入的串行存储是最佳方案。

2.SPI串行FLASH配置电路

SPI串行配置模式常用于已采用了SPI串行FLASH PROM的系统,在上电时将配置数据加载到FPGA中,这一过程只需向SPI串行发送一个4字节的指令,其后串行FLASH中的数据就像PROM配置方式一样连续加载到FPGA中。一旦配置完成,SPI中的额外存储空间还能用于其它应用目的。

1)SPI 配置电路

虽然SPI接口是标准的4线接口,但不同的SPI FLASH PROM芯片采用了不同的指令协议。FPGA芯片通过变量选择信号VS[2:0] 来定义FPGA和SPI FLASH的通信方式、FPGA的读指令以及在有效接收数据前插入的冗余比特数。常用SPI FLASH与FPGA的有效操作配置如表5-3所示,其余的VS[2:0] 配置留有它用。

表5-3 赛灵思芯片所支持的SPI FLASH存储器以及配置列表

从整体上看来,控制SPI串行闪存比较容易,只需要使用简单的指令就能完成读取、擦除、编程、写使能/禁止以及其它功能。所有的指令都是通过4 个SPI 引脚串行移位输入的。

图5-30 支持快读写的串行FLASH配置电路示意图

不同型号的FPGA芯片具有数目不同的从设备片选信号,因此所挂的串行芯片数目也就不一样。例如:Spartan-3E系列FPGA芯片只有1位SPI从设备片选信号,因此只能外挂一片SPI串行FLASH芯片。在SPI串行FLASH配置模式下,M[2:0]=3’b001。FPGA 上电后,通过外部SPI 串行FLASH PROM完成配置,配置时钟信号由FPGA芯片提供时钟信号,支持两类业界常用的FLASH。

图5-30给出了Spartan3E系列FPGA支持0X0B快速读写指令的STMicro 25系列PROM的典型配置电路。其中的Flash芯片需要Flash编程器来加载配置数据;单片的FPGA芯片构成了完整的JTAG链,仅用来测试芯片状态,以及支持JTAG在线调试模式,与SPI配置模式没有关系。

- AT21CS01串行EEPROM与竞品的对比(10-09)

- 读写24LCxx系列的EEPROM的实例程序(02-16)

- DS33Z11/DS33Z44 EEPROM编程指南(09-23)

- Maxim带EEPROM高度集成PMIC MAX17106(02-16)

- DG128的EEPROM问题(02-14)

- 汽车常见EEPROM芯片有哪些?(02-19)