3系列FPGA中使用LUT构建分布式RAM(3)

时间:02-11

来源:网络整理

点击:

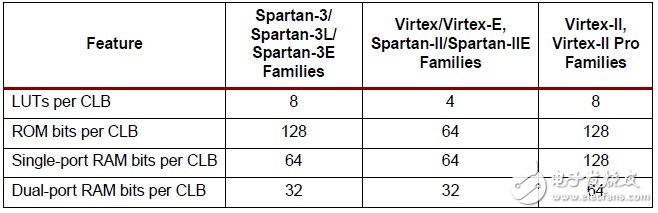

前面简要介绍了Spartan-3系列FPGA中分布式RAM的基本特性。为什么不从更高级的Virtex系列入手呢?我仔细看了一下各个系列的介绍、对比,Spartan系列基本就是Virtex系列的精简版,其基本原理是一样的,所以从简单的入手来融会贯通未尝不是一个好办法。至于各个器件具体的有什么配置,在Xilinx网站上查找它们各自的Datasheet或者User guide即可(这也是资源最近我着重提到的学习资源)。表1给出了Spartan与Virtex系列中分布式RAM的基本对比情况。

表1 Spartan与Virtex系列中分布式RAM的基本对比情况

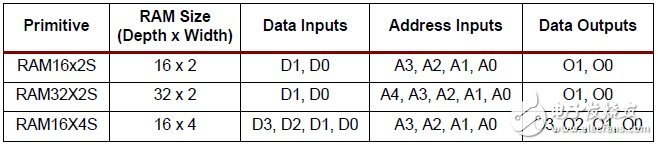

表2 库中分布式RAM的原语

表3 分布式RAM原语的并联使用

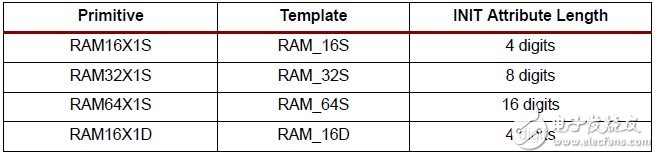

分布式的RAM在器件初始化之后,其内容为全零。如果要求配置为初始化后非零的情况,需要使用INIT属性。每一个INIT都是以16进制编码的矢量,从MSB到LSB排序。表4给出了每个原语的INIT长度。

表4 每个原语的INIT长

每一个Spartan-3 FPGA的CLB都包含4个slice,它们的位置排列datasheet、user guide或者PlanAhead中都可以看到。相比较而言,PlanAhead中的更为直观,可以参考中的图5。分布式RAM仅仅位于SLICEM类型的SLICE中,其中的"M"即表示这种slice支持与存储器相关的函数;而SLICEL中的L表明这种类型的slice仅支持逻辑。- 3系列FPGA中使用LUT构建分布式RAM(2)(02-11)

- 3系列FPGA中使用LUT构建分布式RAM(1)(02-11)

- 3系列FPGA中使用LUT构建分布式RAM(4)(02-11)

- 双RAM技术在LED显示屏控制系统的应用(03-15)

- Xilinx全新参考设计提供业界首个单芯片400G解决方案(02-12)

- FRAM在汽车电子中的应用方案TOP4(02-25)