Verilog代码设计案例分析

时间:02-11

来源:网络整理

点击:

Verilog以其灵活性而得到大部分FPGA设计者的喜爱,然而有些时候,这些灵活性也带来一些小问题,因此我们要记住,电脑永远没人我们聪明,我们一定要提前知道代码会被综合成什么样子。下面举一个有趣的例子。

假如定义如下变量:

reg [4:0] wp;

reg [4:0] rp;

……………………….

……………………….

Always @(posedge rx_ll_clock)

Begin

………………

………………

………………

if (rp == wp + 2)

full <= 1'b1;

else

full <= 1'b0;

…………………..

…………………..

end

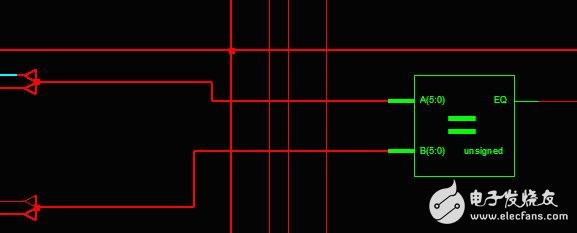

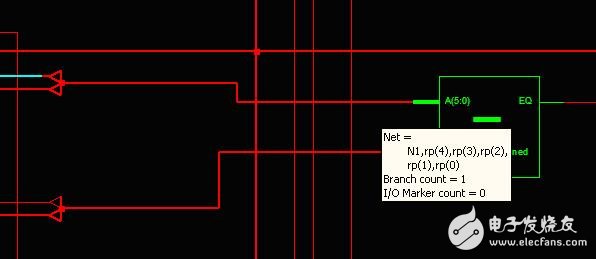

从上面的代码可以看出,综合器应该综合一个触发器,一个加法器和一个比较器。这里的触发器和加法器不多说了,问题就出在的比较器上。按照我们的想法是当rp=0,wp=30时,full应该在时钟沿变为为"1"。在项目设计时,FuncTIon仿真时就出现了问题,最终发现综合器的综合结果和我们预期的不一致,如下图所示.

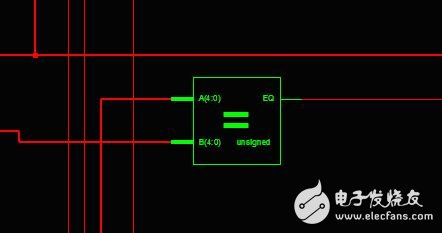

很明显,综合的比较器位宽是[5:0]而不是我们期望的[4:0]。最终我们将红色部分修改如下:

if (rp == wp + 2)改为if (rp == wp + 5’h02)

最终的综合结果变为我们所期望的结果:

- wince代码写入LCD驱动参考,数码产品怎样分别是不是LCD坏点(04-26)

- 赛灵思FPGA DIY系列(2):数字存储扫频仪(11-06)

- FPGA设计:时序是关键(07-15)

- 各种 IP Core和参考设计(04-20)

- MC8051 IP核基本结构及原理(04-22)

- Verilog HDL语言的文件调用问题:include使用方法介绍(02-24)