3系列FPGA中使用LUT构建分布式RAM(2)

时间:02-11

来源:网络整理

点击:

分布式RAM支持以下的单口RAM与双口RAM类型:

带有异步写/同步读的SRAM,其中的同步读取可以使用与分布式RAM相关联的触发器实现。

带有一个同步写端口与两个异步读端口的DRAM,其中同步同步读的原理与前者相同。

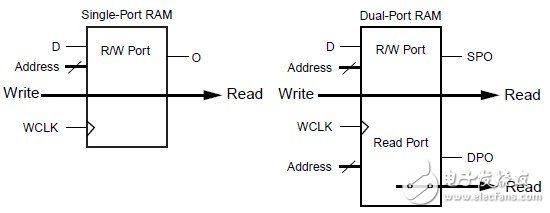

图1给出了SRAM与DRAM的示意,可以看出DRAM有一个读/写端口和一个独立的读端口。任何对D输入端口的写操作和对SPO输出端口的读操作可以同时进行,并且和对另一个读端口即DPO的读操作是互相独立的。

图1 SRAM与DRAM的示意

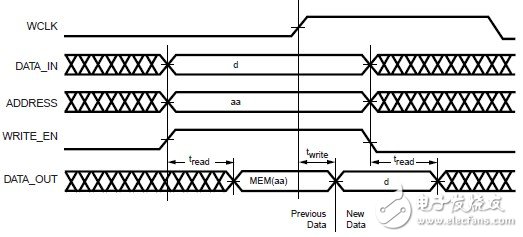

写操作是在写使能信号WE控制下的单时钟沿操作。WE默认是高有效的。当写使能为高时,在时钟沿锁存写地址,并将数据写入所选择RAM区域的D端口。读操作则是纯组合的:单口或者双口模式的地址端口是异步访问的,其延迟时间与LUT是逻辑延迟是一致的。若读、写操作同时发生,则在同步写入信的数据时,输出反映的正在被写入内存单元的数据,这一机制与Spartan-3系列FPGA中块RAM的机制是类似的,在相应的User Guide中被称为"WRITE_MODE=WRITE_FIRST"。图2给出了这种操作的时序图。

图2 读、写操作同时发生时的时序图

总结上面提到的几种操作,可以得到以下特征:一次写操作只需要一个时钟沿。

读操作只需要逻辑读取的时间。

输出是异步的,并且其延只与LUT的逻辑延迟有关。

数据与地址输入被写时钟所存,并且有特定的建立时间要求,但不需要保持时间。

双口RAM的A[#:0]端口是读和写的地址,DPRA[#:0]端口是独立的只读的地址。

- 3系列FPGA中使用LUT构建分布式RAM(1)(02-11)

- 3系列FPGA中使用LUT构建分布式RAM(3)(02-11)

- 3系列FPGA中使用LUT构建分布式RAM(4)(02-11)

- 双RAM技术在LED显示屏控制系统的应用(03-15)

- Xilinx全新参考设计提供业界首个单芯片400G解决方案(02-12)

- FRAM在汽车电子中的应用方案TOP4(02-25)