在ISE中直接调用chipscope进行在线逻辑分析(3)

时间:02-11

来源:网络整理

点击:

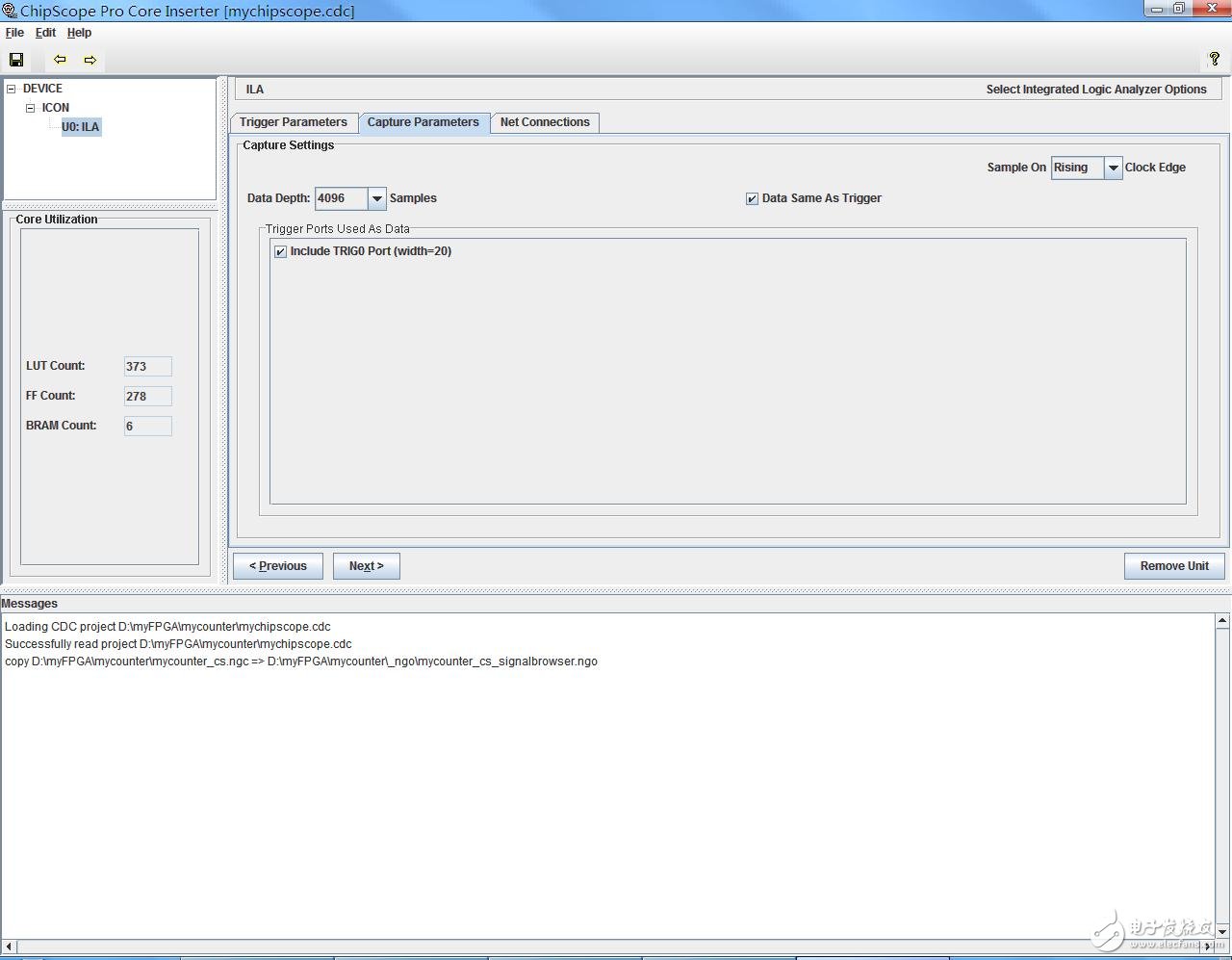

点击Next之后,进入了捕获参数的设计界面,如图4所示。"捕获"的含义自然指的是要被捕捉、观测的数据了。这里的参数ISE一般情况下已经给智能设置好了,所以不需要更改。

图4 捕获参数界面

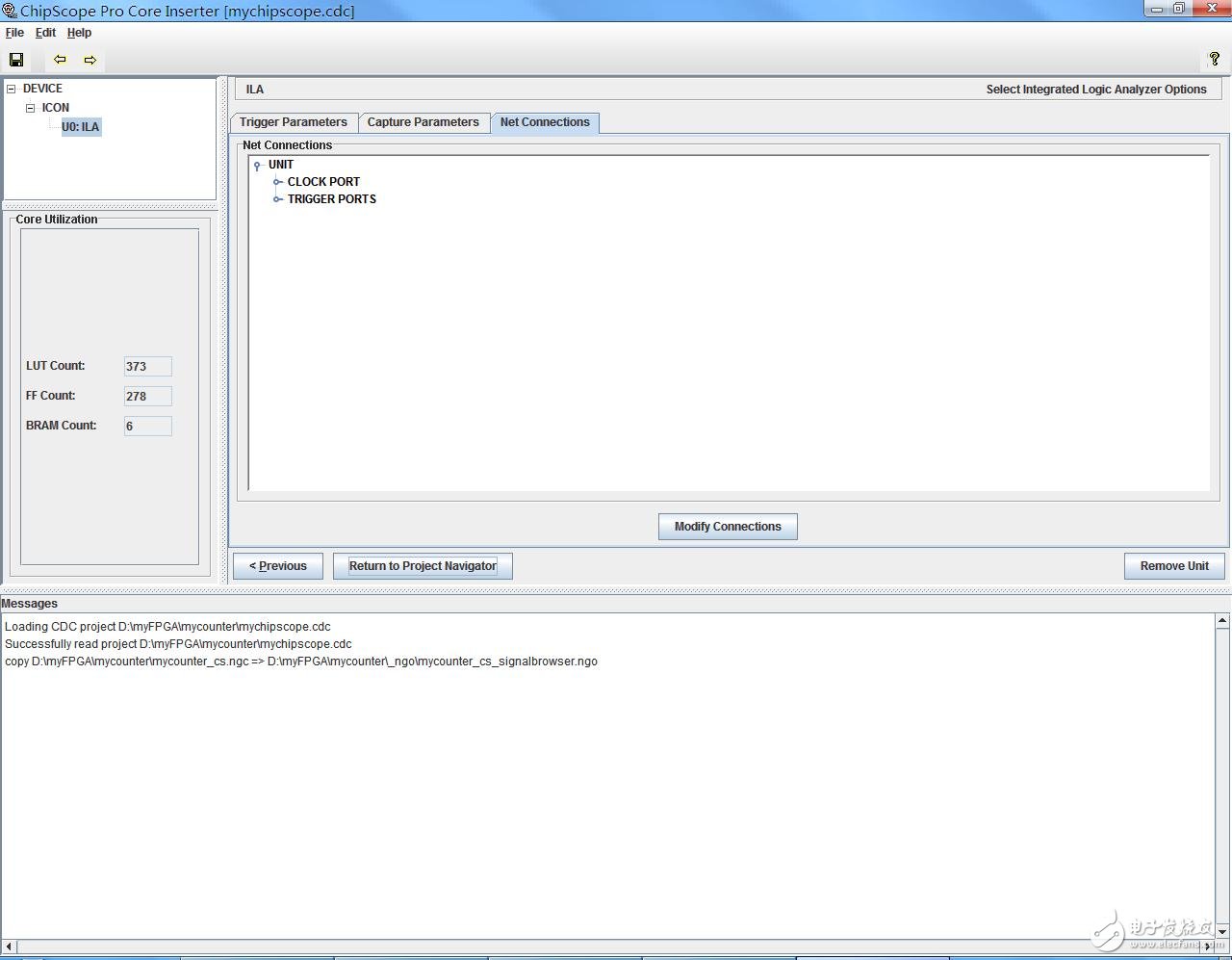

再点击Next之后,进入了网络标号连接参数的设计界面,如图5所示。

图5 网络标号连接界面

这里需要对设计中的网表和Chipscope的核进行连接,点击图中的"Modify ConnecTIons"进入连接界面,分别如图6、图7所示。

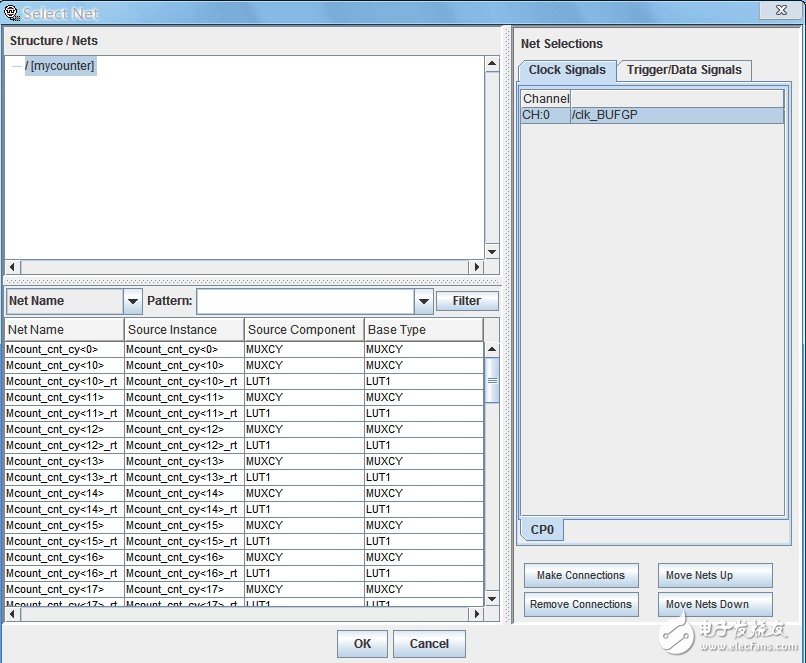

图6 clock设置界面

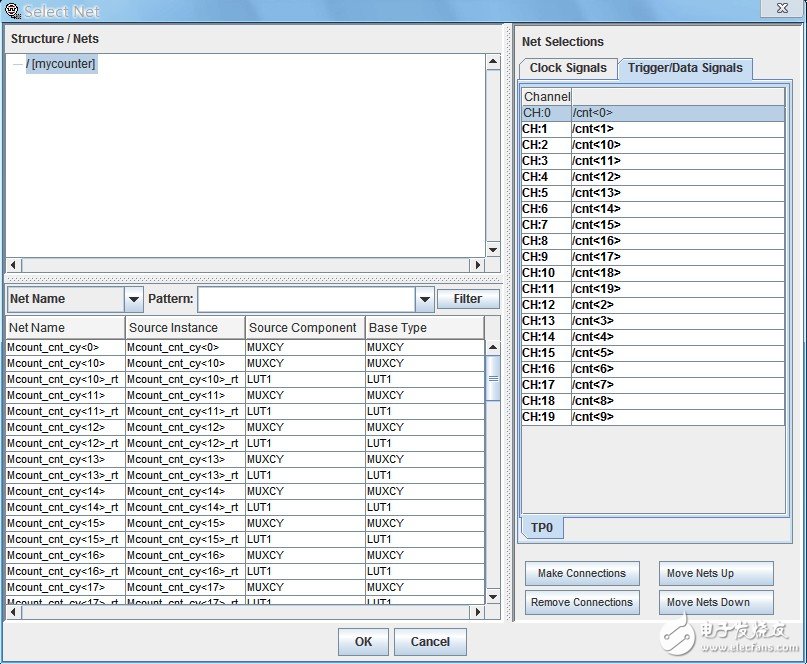

图7 触发/数据信号设置界面

图6的时钟即为系统设置的时钟。点击左侧Net Name中的clk_BUFGP,然后点击右下方的"Make ConnecTIons",即可将clk_BUFGP与Chipscope核中的时钟信号相连接。这里不能直接把clk信号(port类型)直接连接到Chipscope核中的时钟信号,否则Chipscope会报错。具体原因我还不是非常理解,不过即使是在普通的FPGA设计中,也不是直接使用clk来驱动的,而是必须经过clk_BUFGP的缓冲才行,这在综合软件给出的综合网表中容易看到。图7为需要观测的触发/数据信号。顾名思义,将需要被观测的信号与其进行"Make ConnecTIons"就可以了。

完成图6、7的操作之后,点击"OK",会返回Chipscope的主界面。假如有错误或设置不合理的话,在Chipscope的Messages窗口中会给出警告或者错误信息。无误之后点击Chipscope左上角的保存按钮,然后关闭Chipscope主界面,返回ISE Project Navigator。

- Date功能:ISE中如何在未综合实现的前提下打开ChipScope ?(02-10)

- 在ISE中直接调用chipscope进行在线逻辑分析(1)(02-11)

- 在ISE中直接调用chipscope进行在线逻辑分析(2)(02-11)

- 在ISE中直接调用chipscope进行在线逻辑分析(4)(02-11)

- 基于ISE设计提供低功耗FPGA解决方案(09-16)

- ISE联合modelsim功能仿真和综合后仿真(02-10)