静态时序分析基础与应用连载(3)

时间:02-11

来源:网络整理

点击:

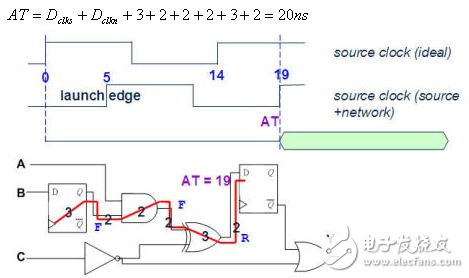

8. 假设前级Flip-Flop的讯号由1变0,计算第2条Path终点的AT。

图二十九

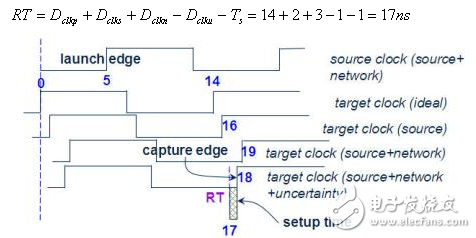

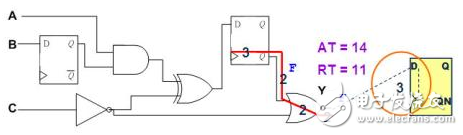

9.计算第2条Path终点的RT

图三十

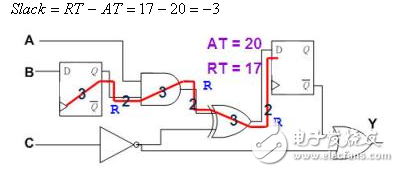

10. 假设前级Flip-Flop的讯号由0变1,计算第2条Path终点的Slack。Slack为负,因此TIming不满足。

图三十一

11. 假设前级Flip-Flop的讯号由1变0,计算第2条Path终点的Slack。Slack为负,因此TIming不满足。

综合10和11,第2条Path的TIming不满足,其Slack为-3。

图三十二

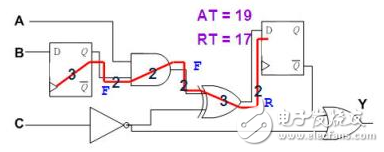

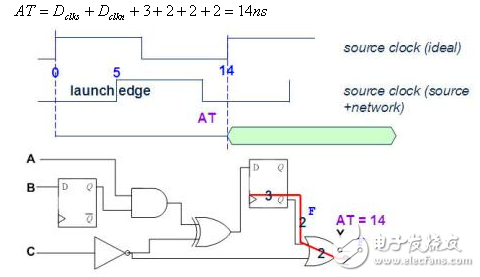

12. 假设前级Flip-Flop的讯号由0变1,计算第3条Path终点的AT。

图三十三

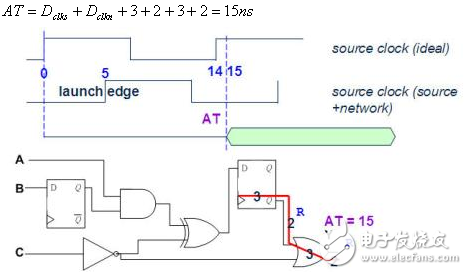

13. 假设前级Flip-Flop的讯号由1变0,计算第3条Path终点的AT。

图三十四

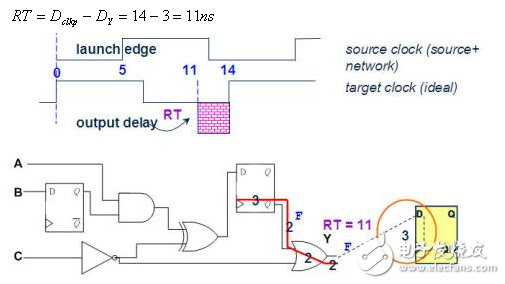

14. 计算第3条Path终点的RT

图三十五

15.假设前级Flip-Flop的讯号由0变1,计算第3条Path终点的Slack。Slack为负,因此TIming不满足。

图三十六

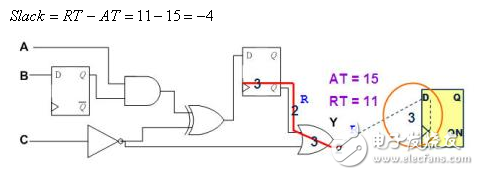

16. 假设前级Flip-Flop的讯号由1变0,计算第3条Path终点的Slack。Slack为负,因此Timing不满足。

综合15和16,第3条Path Timing不符合规格,其Slack为-4。

图三十七

综合上述分析结果,此电路的时序不符合规格,其Critical Path是Path3,Slack为-4。

- 静态时序分析基础与应用连载(2)(02-11)

- 静态时序分析基础与应用连载(1)(02-11)

- FPGA设计:时序是关键(07-15)

- 如何利用FPGA进行时序分析设计(05-21)

- SOC时序分析中的跳变点(08-15)

- 基于GAL的I2C总线时序模拟(02-27)