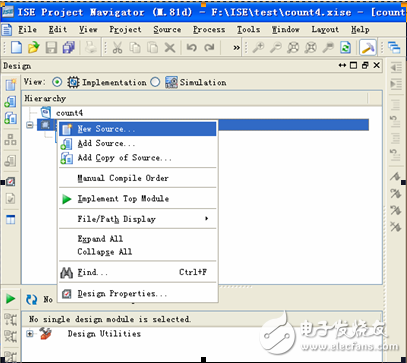

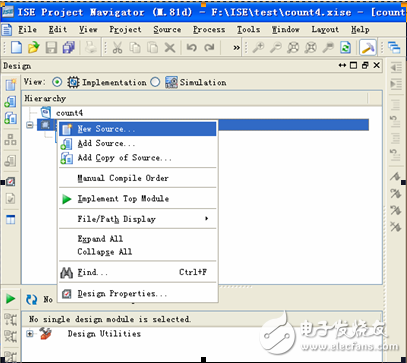

1、代码输入(1)、新建一个ISE工程,名字为count4。(2)、新建一个verilog文件

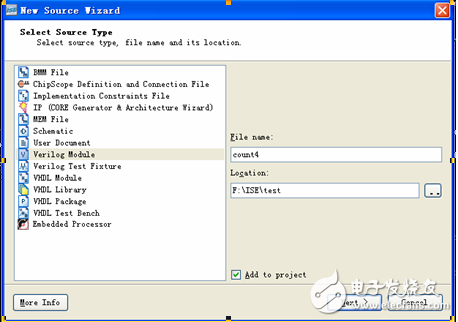

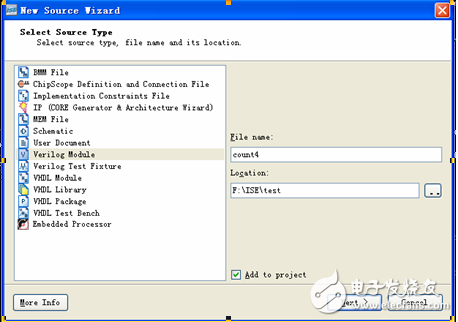

(3)、选择verilog module 输入file name为count4,单击next默认知道finish。

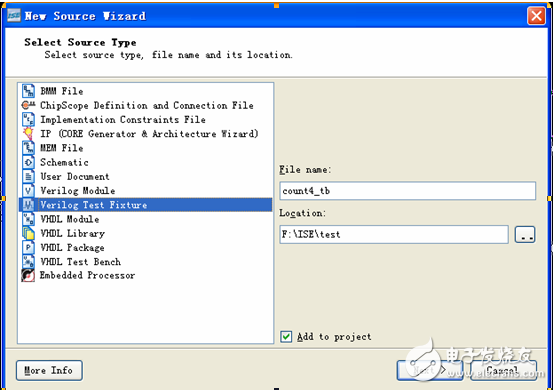

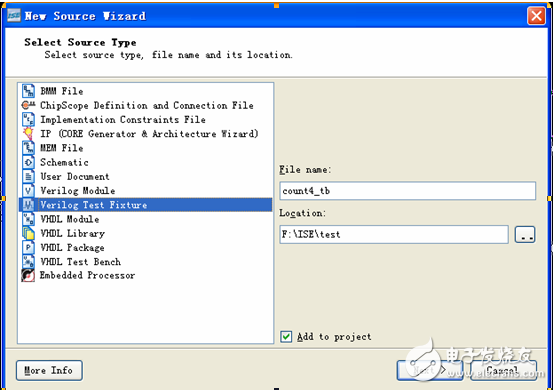

(4)、在count4.v文件中输入以下代码module count4(out,reset,clk ); output [3:0] out; input reset,clk; reg [3:0] out; always@(posedge clk) begin if(reset) out<=0; else out<=out+1; endendmodule(5)、新建一个testbench文件(综合时,不参与综合),和第(2)步骤相同(6)、选择 verilog Test Fixture。

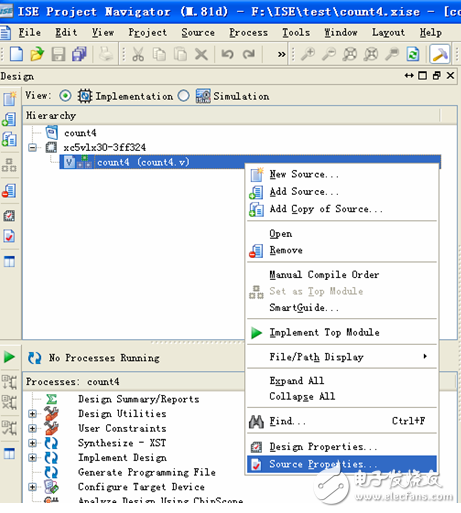

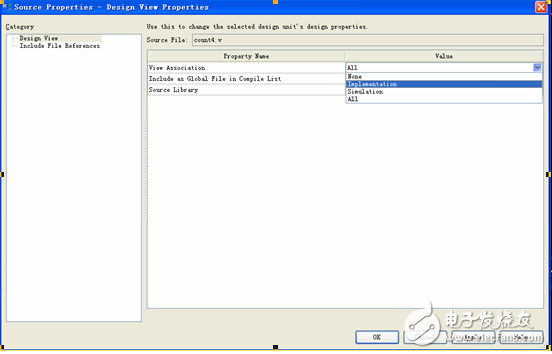

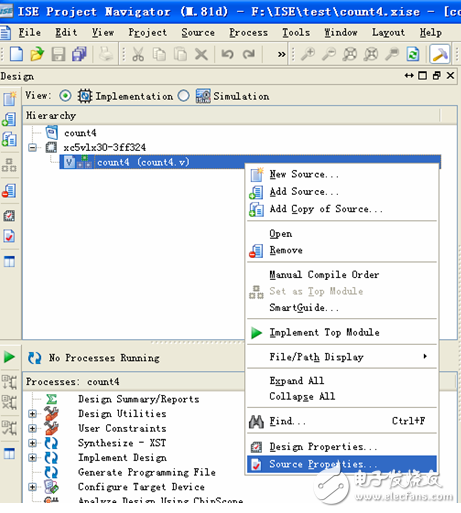

(7)、创建完成后,输入以下代码module count4_tb; reg clk,reset; wire [3:0] out; parameter DELY=100; count4 mycount(.out(out),.reset(reset),.clk(clk)); //count4 mycount(out,reset,clk); 若简写,功能仿真正确,时序仿真会因为端口不匹配,//会出错 always #(DELY/2) clk=~clk; iniTIal begin clk=0; reset=0; #DELY reset=1; #DELY reset=0; #(DELY*200) $finish; end iniTIal $monitor($TIme,,,"clk=%d reset=%d out=%d",clk,reset,out);endmodule注:可以修改文件的属性,是否为testbench或者为verilog文件。右击要修改的文件。选择source properTIes

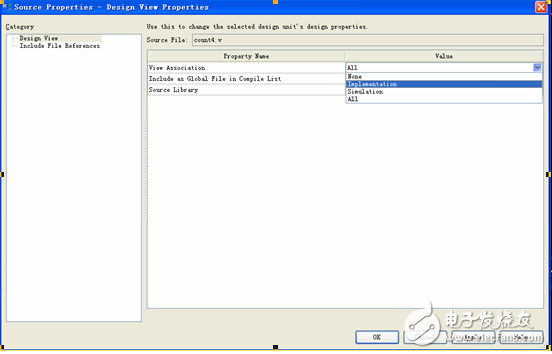

修改属性,simulation为testbench .implementation为正常的verilog文件

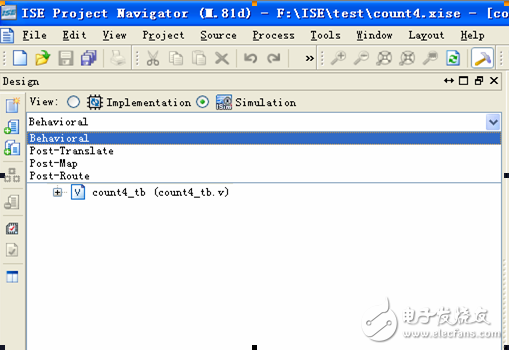

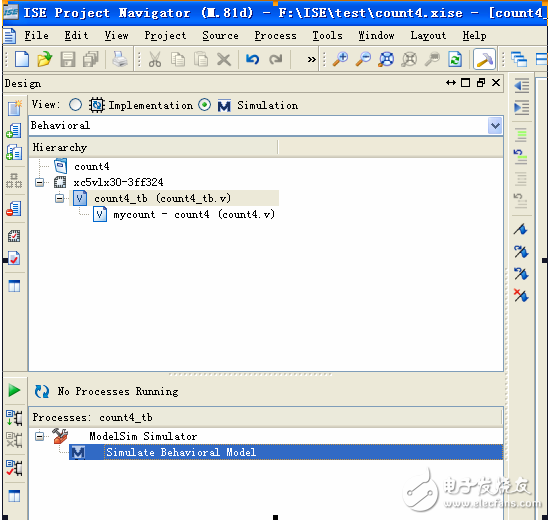

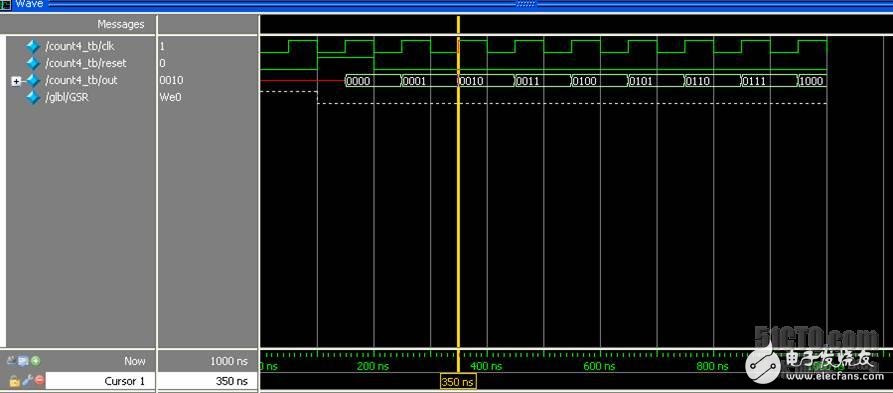

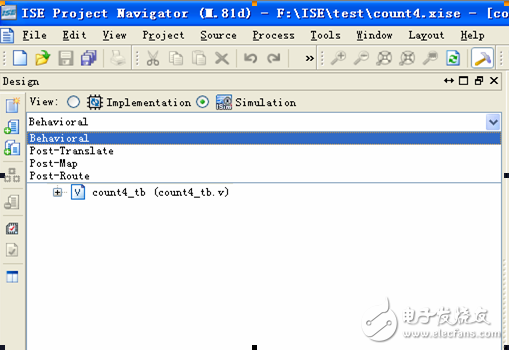

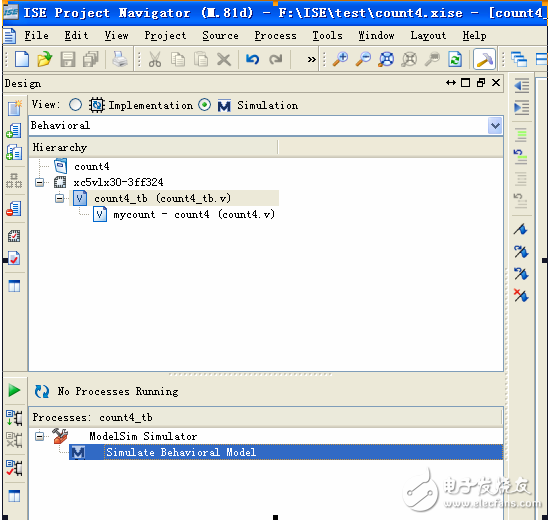

2、功能仿真功能仿真放在综合前面,是因为大型程序综合需要很长的时间,而功能仿真不需要综合,可以先功能仿真,确保代码的正确性。功能仿真正确后,再综合,然后进行综合后仿真。(1)、切换到simulation。选择behavioral。

(2)、单击选中count4_tb文件,然后双击simulate behavioral model。

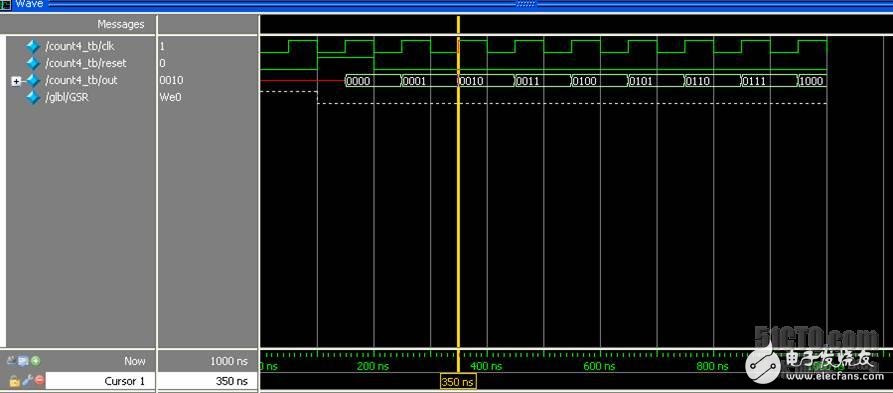

(3)、在modelsim,查看波形等内容。

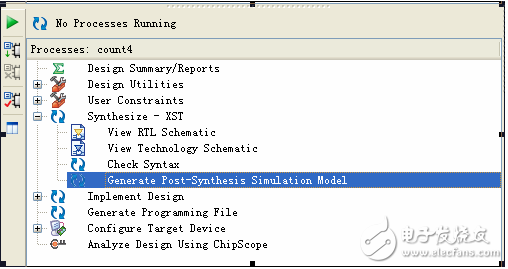

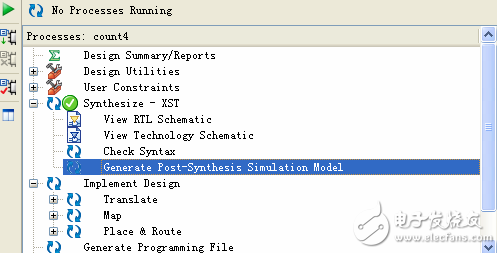

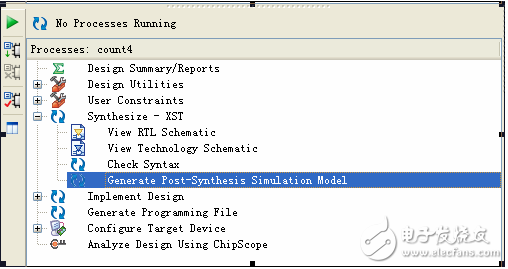

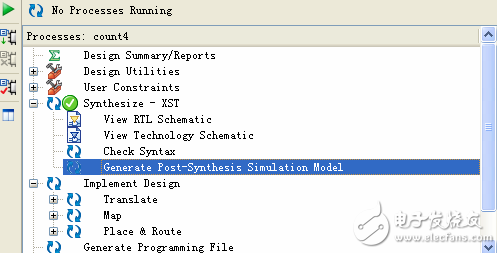

3、时序(综合后)仿真时序仿真将时延考虑进去,包括综合后产生的(与、或、非)门时延,还有布局布线产生的时延。综合(Synthesize),就是将HDL语言设计输入翻译成由与、或、非门和RAM、触发器等逻辑单元组成的网表。综合后可生成综合后仿真模型(Generate Post-Synthesis Simulation Model)。

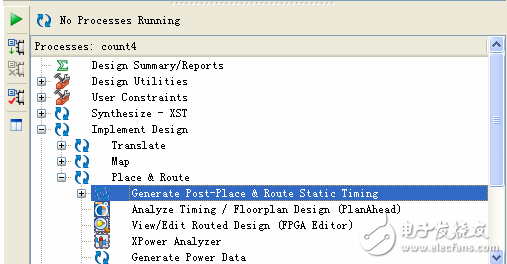

综合后,进行ISE的实现(Implement),包括翻译、映射、布局布线。在这三个过程中都可以生成一个仿真模型(翻译和映射不会产生延时,因此常用布局布线后产生的仿真模型进行时序仿真)

(1)、进行综合,双击 Synthesize – XST ,想生成 Post-Synthesis Simulation Model,双击Generate Post-Synthesis Simulation Model即可,会在工程文件夹下生成netgen\synthesis\count4_synthesis.v等文件

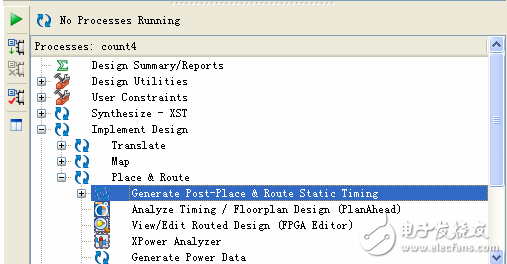

(2)、进行实现,双击 Implement Design ,完成后,双击Generate Post-Place & Route Simulation

(2)、进行实现,双击 Implement Design ,完成后,双击Generate Post-Place & Route Simulation

(2)、进行实现,双击 Implement Design ,完成后,双击Generate Post-Place & Route Simulation

(2)、进行实现,双击 Implement Design ,完成后,双击Generate Post-Place & Route Simulation