Xilinx可编程逻辑器件设计与开发(基础篇)连载35:Spartan

添加总线:可按住Ctrl键,选择多个总线信号,单击右键,选择"Add to Bus"命令,将其组合成相应的总线信号,如DataPort,如图9-43所示。

对信号和总线进行编辑:剪切/复制/粘贴/删除信号和总线,在信号或总线名称上单击右键,选择相应的命令。同时支持Windows组合键操作(剪切命令Ctrl+X,复制命令Ctrl+C,粘贴命令Ctrl+V,删除命令Delete)。

对信号和总线进行放大和缩小。

测量光标:【Waveform】窗口中可以设臵两个光标──X和O。用户可以放臵这两个光标到采集的数据点上。该点的信号和总线状态将在X或者O里显示,两个带颜色的竖线分别为X和O坐标。

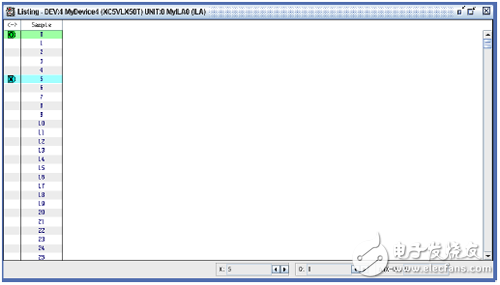

(2) 【Listing】窗口如图9-44所示。

图9-44 【Listing】窗口界面

【Listing】窗口以列表形式显示采样缓冲区。基本功能和【Waveform】相同。

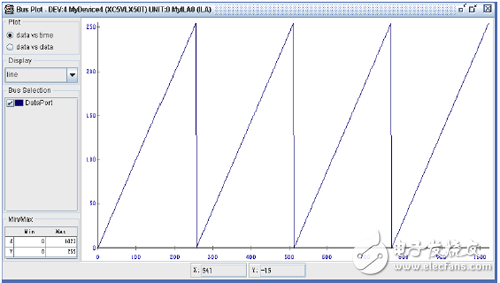

(3) 【Bus Plot】绘图窗口如图9-45所示。

图9-45 【Bus Plot】窗口界面

【Plot】选项组。

【data vs. time】:显示所有的总线,每条总线有单独的颜色,可以根据数据格式(十六进制,二进制,十进制等)显示。

【data vs. data】:需要选择两条总线,x和y坐标分别对应一组总线。

【Display】选项组:图形绘制方式可以是【lines】线、【points】点或者【 lines and points】点线。

【Bus Selection】选项组:选项中列出设臵中所有的总线,根据【Plot】选项组设臵的方式,选择所要观测的总线组。可以单击总线名旁边的【Colored】按钮,选择总线的颜色。

【Min/Max】选项组:显示视图中的最大最小值。

【X】【Y】:显示鼠标所在位臵的x或y坐标。

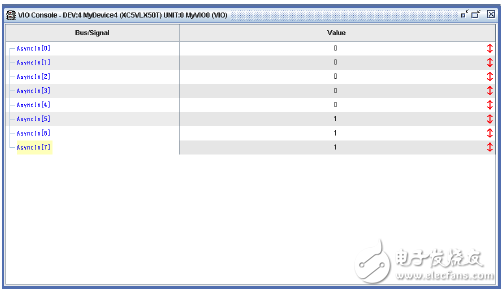

如果设计中有VIO核,可以在【VIO Console】窗口观测虚拟输入输出信号状态,如图9-46所示。

图9-46 【VIO Console】窗口界面

(1) 【Bus/Signal】栏:包含VIO核的总线或者信号名称。单击右键,设置信号/总线的【Type】显示类型和【Persistence】显示时间长度。

【Type】:设臵VIO总线/信号的类型。

VIO输入信号支持的显示类型:

文本:ASCII字符

LEDs(红、蓝、绿三个颜色可选;可以设置为高有效或低有效)

VIO输入总线只支持一个有效显示类型

文本

VIO输出信号支持的显示类型:

文本:ASCII文本

按钮:高有效或低有效

反转按钮

脉冲序列(只针对同步输出)

单脉冲(只针对同步输出)

VIO输出总线就有两个有效显示类型:

文本

脉冲序列(只针对同步输出)

【Persistence】:设臵VIO总线/信号【Value】栏的显示时间长度。

【Infinite】:一直显示VIO总线/信号。

【Long】:显示80个采样周期。

【Short】:显示8个采样周期。

(2) 【Value】栏:显示信号的当前值。

五、 导入、导出数据

ChipScope提供了强大的数据采集能力,最大深度可达16384,单靠肉眼观测是不可行的,需要将采集波形存储下来,再通过VC、MATLAB等工具完成后续分析。【File】菜单下【Export】命令,可导出.VCD、.ASCII以及.FBDT等3种类型的文件。

用户可以对采样信号进行重命名,然后在ChipScope中导入所有信号名,以方便观察和分析。Core Generator、Core Inserter、Synplicity Certify和FPGA Editor 工具都可以产生有关信号名的文件,在ChipScope中,可以运行【File】菜单下【Import】命令,从指定文件中导入信号名。

9.5 利用FPGA Editor修改Chipscope Pro核信号连接

对于使用高密度FPGA实现的复杂的逻辑设计,每次在ChipScope Pro Core中修改信号探点都需要重新进行布局布线,布局布线需要花费较长的时间。更令人头痛的是,布局布线后的结果可能每次都有差异,有时会变得很差。如何解决这个问题呢?FPGA Editor与ChipScope的协同工作有效地解决了这个问题。

利用FPGA Editor和ChipScope Pro协同工作,可在FPGA Editor中对器件内的ChipScope Pro探点直接修改。由于不再布局布线,不仅提高了工作效率,而且ChipScope Pro Analyzer的跟踪和分析也更准确。

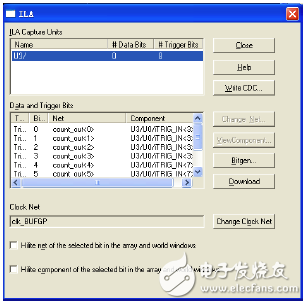

运行ISE 11.x设计工具,在【Processes for Source....】窗口中单击【View/Edit Routed Design(FPGA Editor)】。弹出FPGA Editor界面,在右边菜单栏中单击【ILA】命令,打开如图9-47所示的ILA设计界面,在【Array】窗口中修改布线。

图9-47 【FPGA Editor】ILA设计界面

【ILA Capture Units】列表框:列出了设计中ILA捕获单元的名称和位信息。

【Data and Trigger Bits】列表框:列出了所选ILA捕获单元的类型、位数、网线和部件信息。

【Write CDC..】按钮:保存ChipScope Pro Core的修改为后缀为.c

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)