Xilinx可编程逻辑器件设计与开发(基础篇)连载35:Spartan

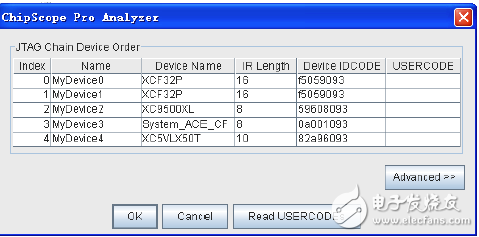

会列出JTAG链上的器件,如图9-39所示。Analyzer能自动识别出边界扫描链上的所有Xilinx的CPLD、FPGA、PROM以及System ACE芯片。图9-39所示为ML505目标板的JTAG链扫描结果。

图9-39 Analyzer边界扫描结果

当JTAG链扫描正确后,菜单项"Device"才能由灰色变为正常。需要注意的是:ChipScope通过JTAG链来观察芯片内部逻辑,因此在生成配置文件时只能利用.bit格式的配置文件,且时钟需要选择"JTAG CLK",选择"CCLK"可能会导致配置失败。

二、 设置触发条件

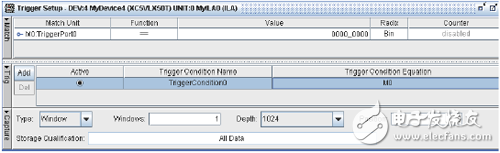

将包含ChipScope核的工程下载到FPGA中以后,还需要设定触发条件才能在Analyzer中捕获到有效波形。Analyzer的触发设置由【Match】匹配、【Trig】触发以及【Capture】捕获三部分组成,其中【Match】用于设置匹配函数,【Trig】用于把一个或多个触发条件组合起来构成复杂的触发条件,【Capture】用于设定窗口的数目和触发位置,典型的配置界面如图9-40所示。

图9-40 Analyzer触发条件配置示意图

(1) 【Match】里设置触发条件的匹配函数,多个函数的组合构成ChipScope Pro核的整个触发条件。

【Match Unit】:用于指定该函数用于哪个触发的匹配函数。

【Function】:选择比较类型。

【Value】:设臵比较的具体数值。

【Radix】:设臵【Value】里的数据格式。可以是十六进制、八进制、二进制、有符号或者无符号数。

【Count】:触发条件所设臵的事件发生多少次之后才认为满足触发条件。

【at least n times】:事件连续或者不连续发生n次后满足触发函数条件。

【for n cycles】:事件只有连续发生n次才算满足触发函数条件。

(2) 【Trig】窗格可以把一个或多个触发条件组合起来,构成复杂的触发条件。触发条件是一个或者多个触发条件的组合,ChipScope Pro根据触发条件判断是否捕获数据。在Analyzer中可以定义多个触发条件。

【Add】按钮:可以加入新的触发条件。

【Del】按钮:可以删除触发条件。

【Trigger Condition Name】:允许用户为触发条件命名。

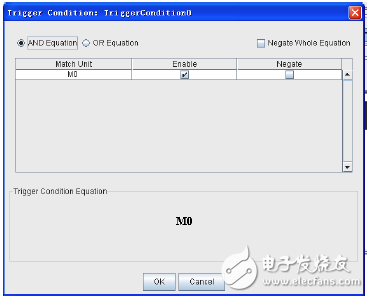

【Trigger Condition Equation】:显示触发条件的构成,默认为来自不同触发条件函数的逻辑与。如果希望改变该设臵,可以单击该区域,弹出【Trigger Condition】对话框,如图9-41所示。可以根据需要设臵,设臵的触发条件等式将重新显示在对话框的下方。在工程管理窗口选择【Trigger Setup】→【Save Trigger Setup】命令,可以将触发设臵保存到后缀为.ctj的文件中,方便下次调用。选择【Trigger Setup】→【Read Trigger Setup】命令,可以从该文件中读入触发条件设臵参数。

图9-41 【Trigger Condition】设置界面

(3) 【Capture】里可以设置视窗的数目和视窗中触发事件的位置,这些视窗通常包含由一个触发事件产生的一连串连续采样点。

【Type】下拉列表框:定义了所用视窗的类型,如果选择【Windows】类型,那么视窗中的采样数必须是2的若干次方,触发可以发生在视窗的任何位臵;选择【N Samples】类型,缓冲器buffer中将包含多个视窗。每个视窗包含N个采样点,每个触发总在第一个采样窗口。

【Windows】编辑框:用来定义窗口的数目,数值范围为1到捕获缓冲区的深度之间。

【Depth】下拉列表框:每个触发窗口的深度,深度由窗口数量决定。

【Position】编辑框:触发位臵,范围为1到捕获缓冲区深度减1之间。

三、 捕获数据

运行捕获Running/Arming the Trigger,设置好触发条件后,在工程管理窗口中选择【Trigger Setup】→【Run】命令,分析仪进入捕获(arm)状态。如果触发条件得到满足,Core捕获数据,直到设置的缓冲区填满为止,然后通过JTAG上传数据,并在【Waveform】和【Listing】窗口中显示。如果需要强制进行数据捕获,可以选择【Trigger Setup】→【Trigger Immediate】命令,该命令忽略触发条件并立刻进行捕获,直到设置的缓冲区填满为止,并在【Waveform】和【Listing】窗口中显示。

要停止捕获,选择【Trigger Setup】→【Stop Acuqisition】命令。

四、 观察信号

ILA核可以通过【Waveform】、【Listing】和【Bus Plot】窗口观察信号波形。

(1) 【Waveform】窗口

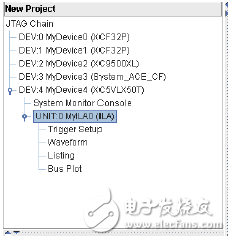

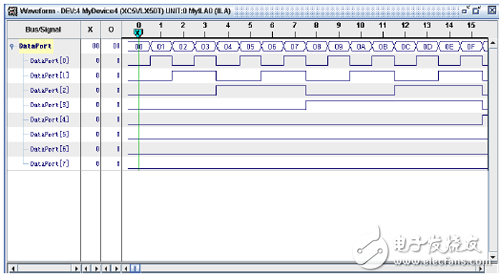

在图9-42所示【JTAG Chain】的ILA核下单击【Waveform】,打开图9-43所示波形显示界面,它类似于逻辑分析仪,可以支持如下操作。

图9-42 观察波形设置

图9-43 Analyzer波形显示界面示意图

重新排列总线和信号的位臵:用户可以拖动信号到所希望的位臵,重新排列总线和信号的位臵。

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)