Xilinx可编程逻辑器件设计与开发(基础篇)连载38:Spartan

PlanAhead允许导入多种不同类型的源文件,包括HDL和NGC核。在RTL编辑器中可以打开、编辑、开发RTL源文件。下面我们介绍【Sources】源文件视图和RTL编辑器的使用。

1. 认识【Sources】源文件视图。

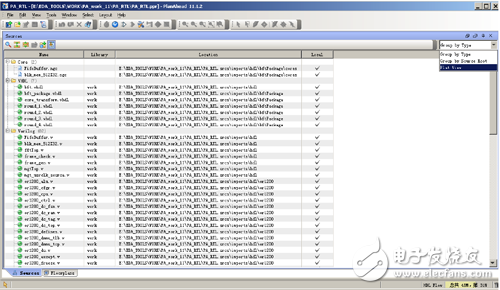

源文件视图显示方式:在【Sources】源文件视图窗口单击,最大化此窗口,如图10-9所示。

图10-9 【Sources】源文件视图—按类型分组

图中【Name】栏显示文件名,其中有三个文件类型Core、Verilog和VHDL。【Library】栏显示相应的源文件属于哪个库。【LocaTIon】栏显示文件路径。【Local】显示导入文件是不是成功。

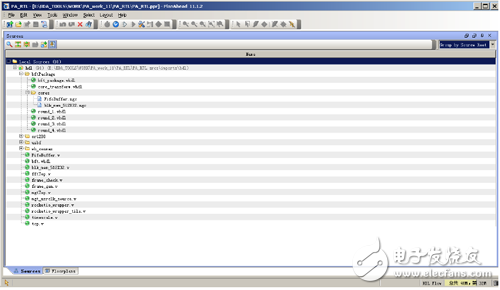

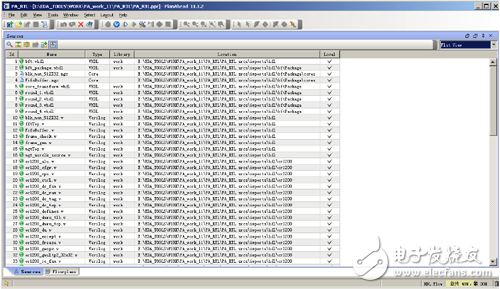

在源文件视图窗口的右上角显示有分组方式,共有4种分组方式,分别是【Group by Type】按类型分组,如图10-9所示,【Group by Source Root】按源文件位置分组,如图10-10所示,【Flat View】打平,按字母顺序分组,如图10-11所示。

图10-10 【Sources】源文件视图—按位置分组

图10-11 【Sources】源文件视图—按字母顺序分组

2. 指定库文件的方法。

在图10-9所示【Sources】源文件视图窗口选择VHDL目录下除了bft.vhdl的文件,单击鼠标右键,在弹出菜单中选择【Set Library…】,在【Set Library】窗口输入bftLib库名。如图10-12所示。这样,就为这几个VHDL文件指定了库文件。

图10-12 【Set Library】窗口

3. RTL源文件编辑器。

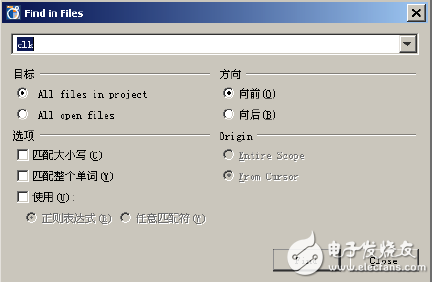

在【Sources】窗口双击HDL文件,就会打开RTL源文件编辑器。在编辑窗口,用右键弹出菜单,设计者可以进行各种编辑操作,例如:删除、复制、查找、替换等。如果单击【Find in File】,出现图10-13所示对话框,键入clk,软件就会找到所有源文件中含有clk的字段,如图10-14所示,选择一个查找结果并双击,会打开相应的源文件,并在源文件中定位。

图10-13 在文件中查找

图10-14 查找结果

三、 创建RTL源文件

在PlanAhead中可以新建HDL源文件,还可以使用语言模板。

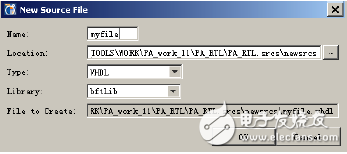

1. 在【Sources】窗口单击鼠标右键,在弹出菜单中选择【Create Source…】打开图10-15所示对话框。输入源文件名,指定存储路径、语言类型和库名。

图10-15 新建源文件对话框

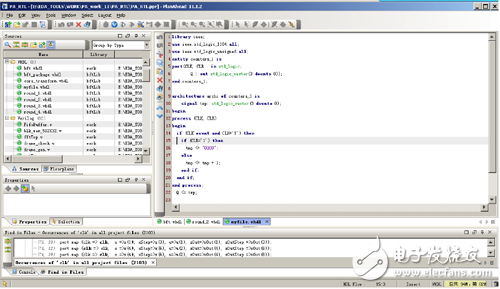

2. 单击【OK】按钮,打开myfile.vhdl窗口,在此窗口空白处单击右键菜单选择【Insert Template…】打开Xilinx语言模板,选择一个模板,例如选择一个计数器,单击【OK】按钮,此模板就会出现在myfile.vhdl文件中,如图10-16所示。当然,设计者可以在这里输入自己的HDL代码。

图10-16 用语言模板创建源程序

四、 探测和分析RTL设计

PlanAhead提供RTL源码探测功能,可以对导入的RTL源码进行编译,编译的错误和警告信息可以被显示出来,可以用这些信息进行交叉定位,很方便地定位到错误或警告源。RTL逻辑层次可以展开,可以用来进行各种分析。一旦使用探测功能,所有RTL视图都允许逻辑对象的交叉探测。RTL网表和层次视图显示了设计的逻辑层次结构。RTL原理图视图允许交互逻辑探测。查找命令可以用来查找逻辑对象。实例属性视图显示了所选实例的信息,包括资源使用信息。RTL DRC工具会告诉设计者设计中哪些地方可以进行功耗和性能优化。

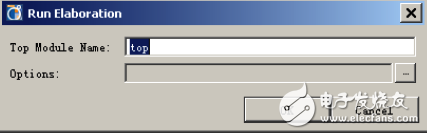

1. 运行RTL探测。在菜单栏选择【Tools】→【Run ElaboraTIon…】,弹出【Run ElaboraTIon】对话框,如图10-17所示,在顶层模块名中输入top,单击【OpTIons】域的浏览按钮,设置综合属性,这里单击【Cancel】,使用默认值,在【Run Elaboration】对话框单击【OK】,开始RTL探测。

图10-17 【Run Elaboration】对话框

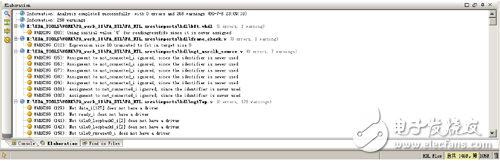

探测结果如图10-18所示。其中有很多Warning,可以单击这些Warning,交叉探测功能会将警告定位在相应的源码中,这样就可以很方便地找到源码中存在的问题。

还可以通过单击【Elaboration】窗口中的图标,切换显示/隐藏Warning信息。如果设计中存在错误,错误信息也会显示在此窗口。

图10-18 【Elaboration】窗口

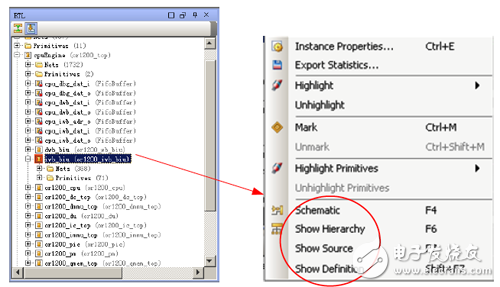

2. 通过RTL网表视图和层次视图检查RTL层次。在图10-19所示的RTL视图中选中一个实例化模块iwb_biu,在右键弹出菜单中选择【Show Definition】、【Show Source】或【Show Hierarchy】,分别会显示功能定义窗口、源代码窗口和层次窗口。图10-20的【Show Definition】窗口显示了所选实例的功能定义文件,图10-21的【Show Source】窗口显示了对所选实例进行例化的位置,图10-22的【Show Hierarchy】窗口显示了所选实例在整个设计中的层次关系。

图10-19 RTL 实例右键弹出菜单

图10-20

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)