Xilinx可编程逻辑器件设计与开发(基础篇)连载32:Spartan

M速率。在【State - Synchronous Sampling】模式,每个信号组数据端口的宽度等于【ATD Pin Count】ATD引脚数和【TDM Rate】TDM速率的乘积。在【Timing – Asynchronous Sampling】模式下,每个信号组数据端口的宽度等于(【ATD Pin Count】ATD引脚数+1)和【TDM Rate】TDM速率的乘积。

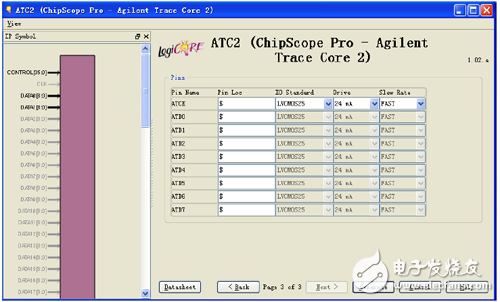

单击【Next】,出现ATC2核ATCK和ATD引脚参数,如图9-13所示。

图9-13 ATC2核ATCK和ATD引脚参数

输出时钟(ATCK)和数据(ATD)引脚在ATC2核内例化,因此用户不用在顶层设计中手动设计,只需在内核产生器中指定这些引脚的位置和属性。这些引脚属性添加在ATC2核的*.NCF文件中。在引脚参数表中,可以设置ATCK和ATD引脚的位置、I/O标准、输出驱动和歪斜率。

(6) Pins选项组。

【Pin Name】:ATC有两类输出引脚:ATCK和ATD。当捕获模式设臵成【State - Synchronous Sampling】模式时,ATCK引脚用作时钟引脚;当捕获模式设臵成【Timing – Asynchronous Sampling】模式时,ATCK和ATD引脚都用作数据引脚。引脚名称是不能改变的。

【Pin Loc】:设臵ATCK或ATD引脚的位臵。

【IO Standard】:设臵ATCK或每个ATD引脚的I/O标准,标准根据器件和驱动器终端类型而定,它和约束文件中定义的I/O标准一样。

【Drive】:设臵引脚输出驱动器的最大输出驱动电流,2~24mA。

【Slew Rate】:设臵ATCK和ATD引脚的信号斜率,FAST或SLOW。

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)