Xilinx可编程逻辑器件设计与开发(基础篇)连载32:Spartan

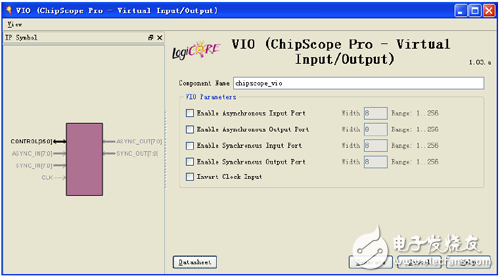

双击【Xilinx Core Generator】,打开现有的IP核工程项目或者创建一个新的IP核工程。【View by funcTIon】→【Debug & VerificaTIon】→【ChipScope Pro】,双击VIO。弹出VIO配置界面,如图9-10所示。

图9-10 VIO参数设置界面

(1) 【Component Name】:输入组件名称。

(2) VIO Parameters选项组:VIO参数选项组。

【Enable Asynchronous Input Port】:使能异步输入信号,最多可以设臵256个异步输入信号,VIO的异步输入用来监测设计中待测试模块的输出信号,它与时钟无关。

【Enable Asynchronous Output Port】:使能异步输出信号,最多可以设臵256个异步输出信号,VIO的异步输出用来为待测试逻辑模块提供输入激励,它与时钟无关。

【Enable Synchronous Input Port】:使能同步输入信号,最多可以设臵256个同步输入信号,VIO的同步输入信号用于监测设计中待测试模块的输出信号,要求待测试信号与VIO核的CLK同步。

【Enable Synchronous Output Port】:使能同步输出信号,最多可以设臵256个同步输出信号,VIO的同步输出信号为待测试模块的输入提供激励,要求待测试信号与VIO核的CLK同步。

【Invert Clock Input】:VIO核可以选择时钟信号翻转,即选择采用时钟的上升沿或者下降沿作为触发条件。

注意:只有使用同步输入和/或输出的时候,时钟信号翻转才有效。

9.2.4 ATC2属性

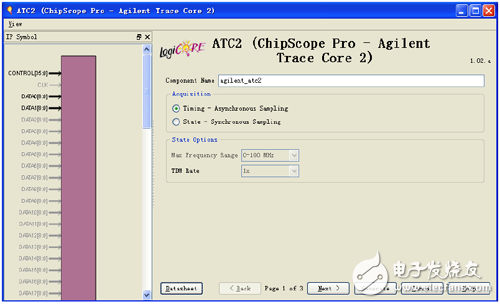

双击【Xilinx Core Generator】,打开现有的IP核工程项目或者创建一个新的IP核工程。【View by funcTIon】→【Debug & VerificaTIon】→【ChipScope Pro】。双击ATC2,弹出ATC2配置界面,如图9-11所示。

图9-11 ATC2参数设置界面

(1) 【Component Name】:输入组件名称。

(2) Acquisition选项组:

【Timing – Asynchronous Sampling】:用于异步数据捕获。数据信号经ATC核输出到FPGA引脚上的通道由组合逻辑组成。

【State - Synchronous Sampling】:用于和CLK输入信号同步的数据捕获。数据信号经ATC核输出到FPGA引脚上的通道由流水线触发器和CLK输入信号组成。

(3) State Options:状态选项组。

【Max Frequency Range】:ATC2核的最大频率范围。有效的最大频率选择项为0~100 MHz, 101~200 MHz, 201~300 MHz和301~500 MHz。当目标数据捕获方式设臵成【State - Synchronous Sampling】,此选择对ATC2核有效。

【TDM Rate】:ATC2核不用片上存储器来存储捕获的数据,Agilent逻辑分析仪通过一个专用探头连接器和FPGA引脚连接传送捕获的数据。ATC2内核数据传送到FPGA引脚上的速率可以与ATC2输入端口DATA的速率相同(TDM速率=1x)或者是DATA速率的2倍(TDM速率=2x)。只有当目标数据捕获方式设臵成【State - Synchronous Sampling】时,TDM速率才可以设臵成2倍数据速率。

设置好后,单击【Next】,弹出引脚设置界面,如图9-12所示。

图9-12 ATC2核ATCK和ATD引脚参数

(4) Pin Settings选项组:引脚设置选项组。

【Enable Auto Setup】:使能Agilent逻辑分析仪自动设臵ATC2核引脚和逻辑分析仪POD的连接。这个属性使得Agilent逻辑分析仪能自动设定每个ATC2引脚的最佳相位和电压采样偏移量。缺省为使能状态。

【Enable Always On Mode】:用于强制ATC2核使能ATC2核内部逻辑和输出缓冲器。FPGA配臵完成后,该模式强制选择BANK0。在该模式下,不通过手动设臵ATC2核,器件在配臵完成之后就可以立即捕获事件。只有当目标数据捕获方式设臵成【TIMING】方式时,该选项设臵才有效。

【ATD Pin Count】:设臵ATD输出引脚数量,范围是4~128。

【Driver Endpoint Type】:用于设臵控制ATCK和ATD输出引脚的输出驱动器类型:单端或者差分。所有的ATCK和ATD引脚必须设臵成相同的驱动器终端类型。

【ATD drivers same as ATCK】:可以修改ATCK引脚参数,如I/O标准、SLEW参数和驱动强度等,并强制ATD驱动器参数与ATCK的驱动器参数保持一致。

【ATD drivers different than ATCK】:可以单独设臵ATD的每一个引脚的驱动器参数,完全独立于ATCK。

(5) Signal Bank选项组:Signal Bank设置选项组。

【Signal Bank Count】:ATC2核包含了一个实时可选的数据信号组多路选择器。该选项代表了多路复用器输入,即数据输入端口数量或者信号分组的数量。有效的信号分组值为1、2、4、8、16、32和64。

【Signal Bank Width】:设臵信号组宽度。ATC2核的每个输入信号组数据端口的宽度取决于捕获模式及TD

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)