Xilinx可编程逻辑器件设计与开发(基础篇)连载45:Spartan

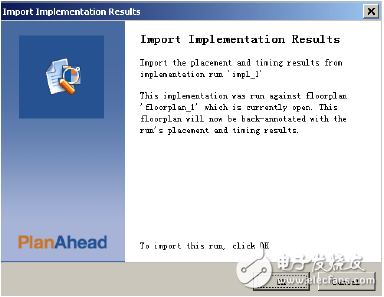

和时序结果,单击【OK】按钮,impl_1 的实现结果会被反标注到设计中。如图10-101 所示。

图10-101 【Import Implementation Results】对话框

(4) 单击图10-101 中的【OK】按钮,会弹出一个确认对话框,如图10-102,单击【确定】按钮,impl_1 的实现结果会被反标注到设计中。同时,图10-103 所示【Device】窗口会显示这一实现结果。

图10-102 属性更改确认对话框

图10-103 【Device】窗口显示的impl_1实现结果

6. 产生.bit位流文件。

在【Design Run】窗口选中impl_1,在右键菜单中选择运行【Run Bitgen】命令,弹出图10-104所示对话框,单击【OK】按钮,生成.bit文件。

图10-104 【Run Bitgen】对话框

7. 启动ChipScope分析仪。

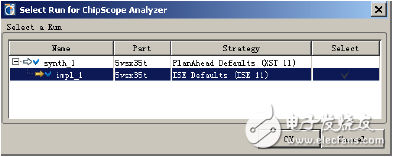

在【Design Run】窗口选中impl_1,在右键菜单中选择运行【Launch ChipScope Analyzer】命令,弹出图10-105所示对话框,选择impl_1(如果设计中运行产生了多个实现结果,这里会显示多个实现),单击【OK】启动ChipScope分析器。使用ChipScope分析仪的步骤请参考相关章节,这里不再赘述。

图10-105 【Select Run for ChipScope Analyzer】对话框

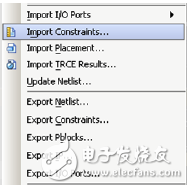

在PlanAhead的【File】菜单栏有一些导入导出功能。设计者可以导入I/O引脚文件、约束文件、位置约束文件、时序文件以及更新网表。设计者可以将PlanAhead的实现结果,通过运行【Export Netlist…】导出EDIF格式的网表文件,运行【Export Constraints…】导出相关的约束文件,然后将这两个文件导入ISE中进行布局布线等后续操作。还可以导出Pblock文件、IP文件、I/O端口文件等。

图10-106 【File】菜单的导入输出功能

10.9 小结

本章重点介绍了如何在PlanAhead中进行RTL源代码开发与分析,如何进行I/O规划,如何进行时序分析,如何进行布局规划,以及在PlanAhead中如何使用ChipScope逻辑分析工具。在PlanAhead中导入综合网表、约束文件以及ISE的布局布线结果的操作流程与上述介绍的过程类似,这里不再赘述。有兴趣的读者可以参考Xilinx相关的设计文档。

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)