Xilinx可编程逻辑器件设计与开发(基础篇)连载45:Spartan

本节将简单介绍在PlanAhead工具中如何应用ChipScope核和分析工具进行逻辑调试与验证。先通过一个向导将ChipScope核插入设计中,选择待测试的网线,并进行例化、连接和综合,最后,导入布局和时序报告,产生位流文件,用ChipScope分析器进行验证。

1. 打开项目。

(1) 运行PlanAhead,在目录"PlanAhead_Tutorial\Projects\project_cpu_hdl"下找到"Project_cpu_hdl.ppr"项目并打开,PlanAhead窗口显示如图10-86所示。

图10-86 【PlanAhead】窗口

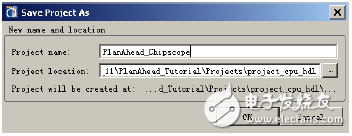

(2) 将项目存储为另外一个项目,以确保原始项目不被损坏。运行【File】→【Save Project as】,打开【Save Project As】对话框,按图10-87中所示设置项目名和项目存储路径。

图10-87 设置项目名和存储路径

2. 应用【Set Up ChipScope】向导。

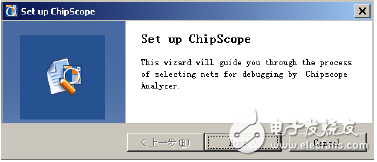

(1) 【Set Up ChipScope】向导引导设计者在综合后网表中插入ChipScope的ICON核和ILA核,并选择待测网线,设置插入的ChipScope核的数目,然后例化这些核,最后将所选网线和核连接起来。

(2) 运行【Tools】→【Set Up ChipScope】向导,将wbArbEngine/m0/wb*网线连接到ChipScope核。如图10-88所示。

图10-88 【Set Up ChipScope】窗口

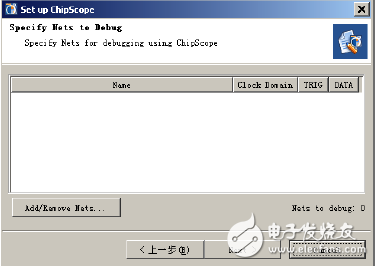

(3) 单击【Next】,出现图10-89所示的【Specify Nets to Debug】窗口。

图10-89 【Specify Nets to Debug】对话框

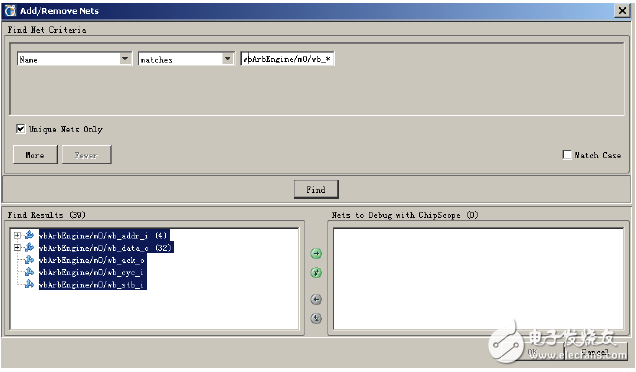

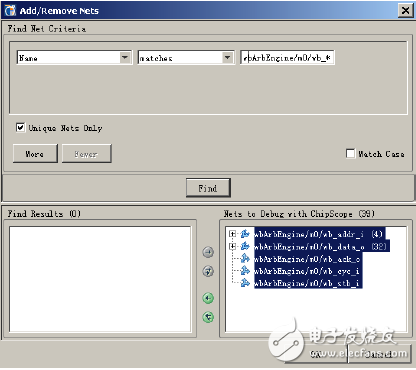

(4) 单击【Add/Remove Nets】按钮,出现图10-90所示【Add/Remove Nets】对话框,按照图中所示设置查找匹配条件为wbArbEngine/m0/wb_*,单击【Find】按钮,查找结果会显示在【Find Results】中。

图10-90 查找结果

(5) 单击按钮,将查找到的网线选为待测试网络,如图10-91所示。单击【OK】退出网线设置对话框。

图10-91 加入待测网线

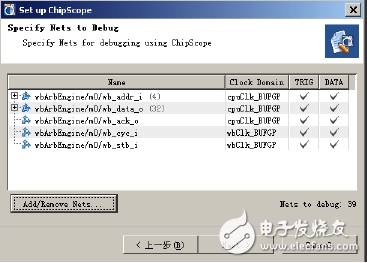

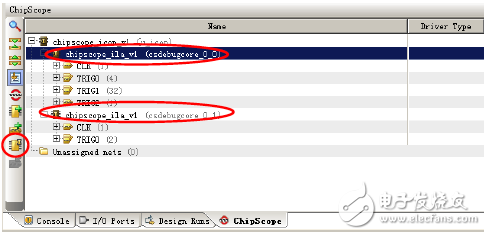

(6) 单击【OK】退出网线设置对话框。这时的【Specify Nets to Debug】对话框显示如图10-92所示,可以看到,共加入了39个需要测试的网线。单击【Next】按钮,出现【Set Up ChipScope Summary】对话框,单击【Finish】,在PlanAhead的【Netlist】窗口可以看到添加了ChipScope核后增加了csdebugcore_0_0、csdebugcore_0_1和u_icon,如图10-93所示。

图10-92 加入网线后的【Specify Nets to Debug】对话框

图10-93 增加了ChipScope 核的【Netlist】窗口

3. 修改ChipScope 核和触发信号的属性。

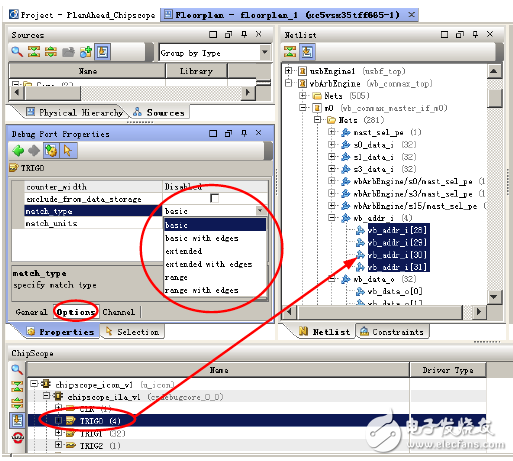

如图10-94 所示,在【ChipScope】视图选择一组触发信号TRIG0,在【Debug Port ProperTIes】中选择【OpTIons】选项卡,可以改变match_type 属性,选择不同的触发条件。

图10-94 改变触发属性

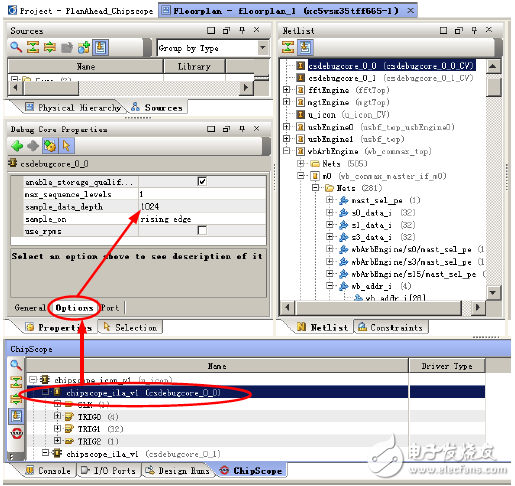

如图10-95 所示,在【ChipScope】视图选择ChipScope 的ILA 核,在【Debug Core ProperTIes】中选择【OpTIons】选项卡,在这里可以修改该核的属性,例如采样深度和采样时钟边沿。

图10-95 改变ChipScope 核属性

4. 实现ChipScope 核。

在图10-96 所示【ChipScope】视窗选择一个ILA 核,单击按钮,实现ChipScope 调试核【Implement ChipScope Debug Cores】,这个命令调用COREGen 工具,将黑盒子ChipScope 调试核转换成综合后ChipScope 核,然后就可以对其进行翻译、映射、布局布线。

图10-96 实现ChipScope 核

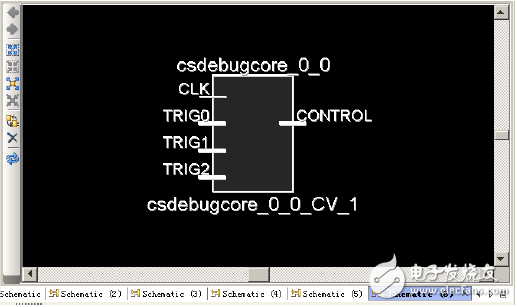

另外, 读者可以在【ChipScope 】窗口选择一个ILA 核, 单击鼠标右键选择【Schematic】,可以看到ChipScope 核的原理图模块,如图10-97 所示。

图10-97 【Schematic】窗口

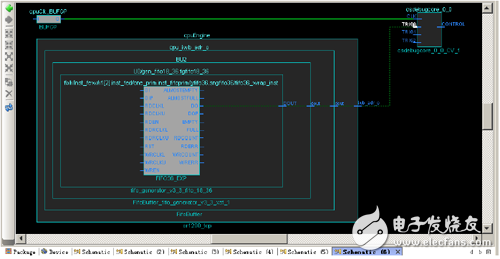

在【Schematic】窗口双击CLK和TRIG0引脚,再单击按钮,重新生成原理图,如图10-98所示。可以看到,TRIG0连接到了设计中的cpuEngine的地址端,这些信号由cpuClk时钟控制。

图10-98 【Schematic】窗口

需要注意的是,在设计中插入ChipScope核,会影响实现结果。因此建议将触发器的输出作为测试点,并且使用区域约束(在PlanAhead中用Pblock),将ChipScope核与关键路径约束在一起,使ChipScope核对时序的影响降至最小。

5. 实现设计。

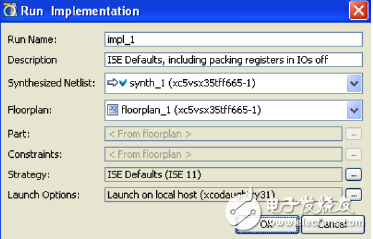

(1) 单击工具栏的运行实现图标,出现【Run Implementation】对话框,如图10-99所示,按图中所示设置各参数。

图10-99 【Run Implementation】对话框

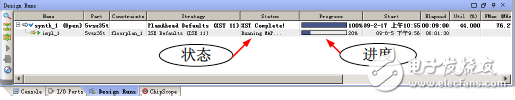

(2) 单击【OK】按钮,【Design Runs】窗口会增加impl_1 进程,如图10-100 所示,该实现进程会简要显示图10-99 所示的设置,并且会显示出该实现的当前状态及进度信息。

图10-100 【Design Runs】窗口

(3) 运行结束后,双击impl_1 进程,弹出【Import Implementation Results】对话框,提示是否导入impl_1 的布局

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)