verilog语言实现任意分频

时间:02-11

来源:网络整理

点击:

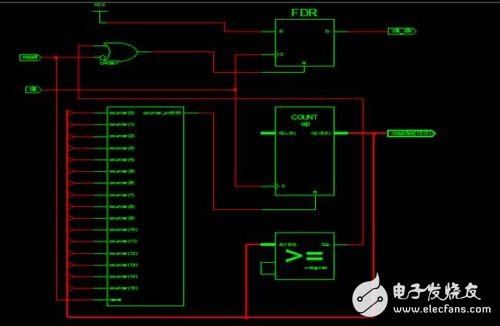

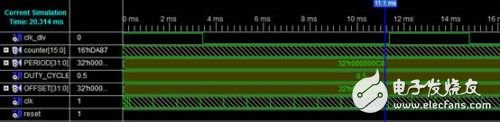

这样的话,对于程序有一定的要求,现在在前面两个实验的基础上做一个简单的总结,实现对一个频率的任意占空比的任意分频。比如: FPGA系统时钟是50M Hz,而我们要产生的频率是880Hz,那么,我们需要对系统时钟进行分频。很容易想到用计数的方式来分频:50000000/880 = 56818。显然这个数字不是2的整幂次方,那么我们可以设定一个参数,让它到56818的时候重新计数就可以实现了。程序如下:module div(clk, clk_div);input clk;output clk_div;reg [15:0] counter;always @(posedge clk)if(counter==56817) counter <= 0;else counter <= counter+1;assign clk_div = counter[15];endmodule分频的应用很广泛,一般的做法是先用高频时钟计数,然后使用计数器的某一位输出作为工作时钟进行其他的逻辑设计,上面的程序就是一个体现。下面我们来算一下它的占空比:我们清楚地知道,这个输出波形在counter为0到32767的时候为低,在32768到56817的时候为高,占空比为40%多一些,如果我们需要占空比为50%,那么我们需要再设定一个参数,使它为56817的一半,使达到它的时候波形翻转,就可以实现结果了。程序如下:module div(clk, clk_div);input clk;output clk_div;reg [14:0] counter;always @(posedge clk)if(counter==28408) counter <= 0;else counter <= counter+1;reg clk_div;always @(posedge clk) if(counter==28408) clk_div <= ~clk_div;endmodule继续让我们来看如何实现任意占空比,比如还是由50 M分频产生880Hz,而分频得到的信号的占空比为30%。56818&TImes;30%=17045module div(clk,reset,clk_div,counter);input clk,reset;output clk_div;output [15:0] counter;reg [15:0] counter;reg clk_div;always @(posedge clk)if(!reset) counter <= 0;else if(counter==56817) counter <= 0;else counter <= counter+1;always @(posedge clk)if(!reset) clk_div <= 0;else if(counter<17045) clk_div <= 1;else clk_div <= 0;endmoduleRTL级描述:

- 电子电路设计之C51单片机常见问题(10-22)

- 电子电路常见故障类型及处理方法系统解析(08-22)

- 那些值得电子发烧友珍藏的经典模拟电路(02-03)

- 基于MC8051 IP核和FPGA的频率计设计(11-24)

- 赛灵思FPGA DIY系列(2):数字存储扫频仪(11-06)

- 基于Verilog FPGA 流水灯设计(07-09)