Xilinx DDR3控制器接口带宽利用率测试(二)

时间:02-11

来源:网络整理

点击:

一.单Bank多行切换测试:

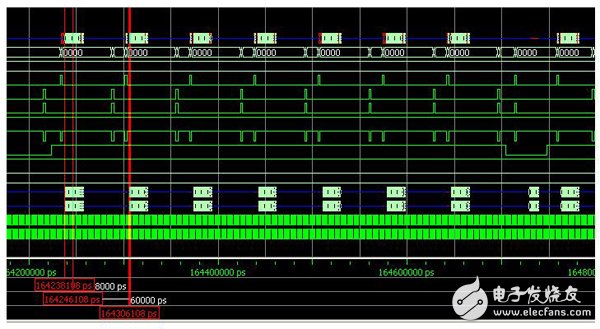

描述:单Bank内行切换时,每次打开一个Row,进行一次写操作以后,必须重新打开另外一个Row,才能进行该Row的写操作。两个Row打开操作有时间间隙要求,打开Row到写操作也有时间间隙要求。因此导致单Bank内行切换时,带宽利用率极低。图中每个写操作中8个数据有效,后8个数据无效。因此,在一个写操作所占用的时间内,有效时间仅有8ns,无效时间为60ns,导致总的带宽利用率仅为8/68=11.8%。

图2 单Bank多行切换时序图

二.两Bank不换行平滑过渡测试

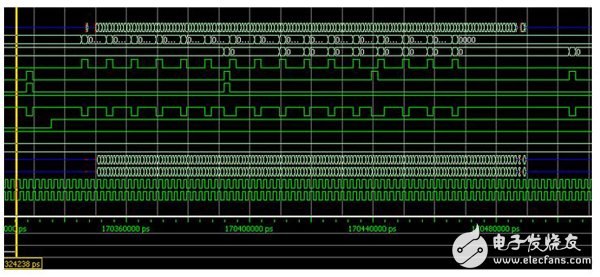

描述:先在Bank0的同一个Row内连续写8次然后过渡到Bank1的同一个Row内连续写8次。可以在Bank0的写操作过程中打开Bank1的一个Row,而不影响Bank0的写操作。由于提前了足够的时间打开Bank1,那么等Bank0的写操作结束后,可以直接平滑的过渡到Bank1的写操作阶段,中间没有等待。在不考虑DDR3的定时充电对带宽的消耗,以及读写切换对带宽的消耗,这种工作模式的带宽利用率接近100%。这种应用模式很适合于数据的连续缓存,可以使带宽利用率最大化。

图3 两Bank不换行平滑过渡时序图

- Xilinx Kintex UltraScale 一半尺寸的 PCI Express 平台 (HTG-K816)(06-15)

- Xilinx全新参考设计提供业界首个单芯片400G解决方案(02-12)

- Xilinx用于工业自动化的机器视觉解决方案(11-30)

- Xilinx多协议机器视觉摄像机参考设计(12-01)

- 机器视觉技术原理解析及解决方案集锦(02-06)

- 机器视觉在汽车电子方向的应用解决方案(02-13)