基于Xilinx FPGA的通用信号采集器

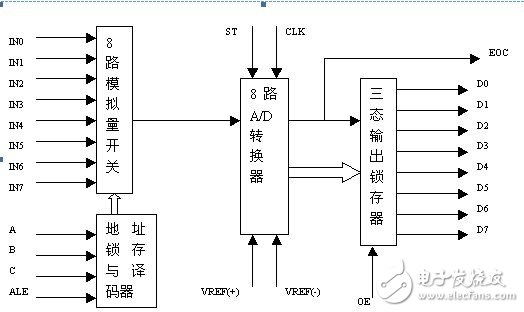

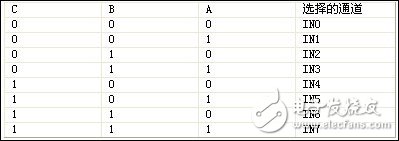

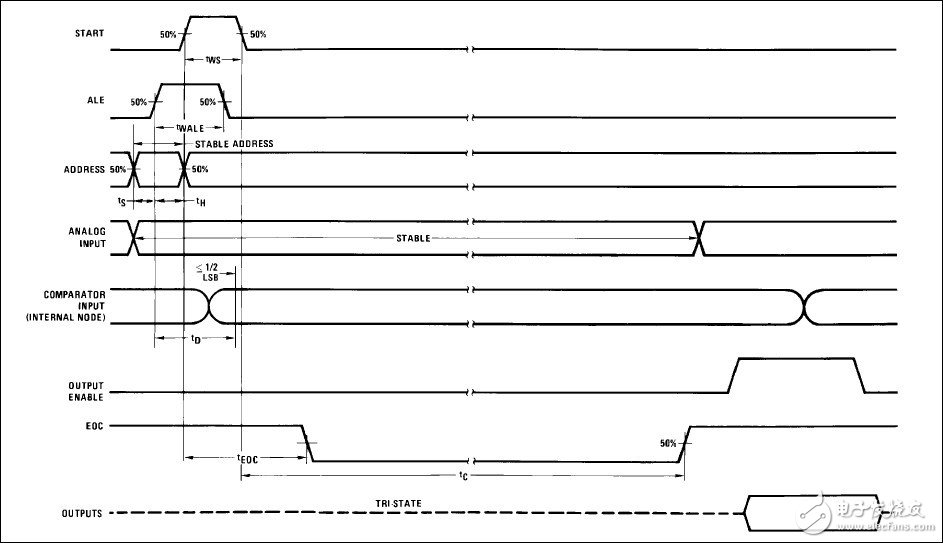

上一篇写了基于Xilinx FPGA的通用信号发生器的案例,反响比较好,很多朋友和我探讨相关的技术,其中就涉及到信号的采集,为了使该文更有血有肉,我在写一篇基于Xilinx FPGA的通用信号采集器,望能形成呼应,以解答大家的疑问。目的:1.通过设计实现信号采集与分析,掌握组合逻辑设计方法;2.通过设计实现信号的采集与分析,掌握信号采集原理。原理:利用FPGA芯片,用verilog语言编写逻辑,控制AD0809进行AD转换。AD0809是带有8位AD转换器、8路多路开关以及微处理机兼容的控制逻辑的CMOS组件,它是逐次逼近式的AD转换器。AD0809的内部结构图如下:

123456789101112131415161718192021222324252627282930313233343536373839404142434445464748495051525354555657585960616263646566676869707172737475767778798081828384858687888990919293949596979899100101102103104105106107108109110111112113114115116117118119120121122123124125126127128129130131132133134135136137138139140141142143144145146147148149150151152153154155156157158159160161162163164165166167168169170171172173174175176177178179180181182183184185186187188189190191192193194195196197198199200201202203204205206207208209210211212213214215216217218219220221222223224225226227228229230231232233234235236237238239240241242243244245246247248249250251252253254源代码1.Verilog源代码,dataCollect.vmodule dataCollect(sysclk, rst, adda, addb, addc, start, oe, datain, led_sel, led_seg); input sysclk, rst; input wire [7:0] datain; output reg adda, addb, addc, start, oe; output reg[3:0] led_sel; output reg[7:0] led_seg; reg [3:0] counter1; reg [7:0] readdata; reg [9:0] counter2; reg [15:0] sum; reg [7:0] averdata; reg [7:0] temp; reg [3:0] dataout1, dataout2, dataout3; reg [3:0] counter3; parameter ZERO = 8'b11111100,ONE = 8'b01100000, TWO = 8'b11011010; parameter THREE = 8'b11110010, FOUR =8'b01100110; parameter FIVE = 8'b10110110, SIX = 8'b10111110, SEVEN =8'b11100000; parameter EIGHT = 8'b11111110, NINE = 8'b11110110, BLANK = 8'b00000000; always @(posedge sysclk or negedge rst) begin if (!rst) begin adda = 0; addb = 0; addc = 0; oe = 1; counter1 = 0; end else begin counter1 = counter1 + 1; case (counter1) 3 : start = 0; 4 : start = 1; 5 : start = 0; 10 : readdata = datain; 15 : counter1 = 0; default : counter1 = counter1; endcase end end always @(posedge sysclk or negedge rst) begin if (!rst) begin counter2 = 0; sum = 0; averdata = 0; end else begin counter2 = counter2 + 1; if ((counter2%16) == 0) sum = sum + readdata; else if (counter2 > 512) begin averdata = sum / 32; sum

123456789101112131415161718192021222324252627282930313233343536373839404142434445464748495051525354555657585960616263646566676869707172737475767778798081828384858687888990919293949596979899100101102103104105106107108109110111112113114115116117118119120121122123124125126127128129130131132133134135136137138139140141142143144145146147148149150151152153154155156157158159160161162163164165166167168169170171172173174175176177178179180181182183184185186187188189190191192193194195196197198199200201202203204205206207208209210211212213214215216217218219220221222223224225226227228229230231232233234235236237238239240241242243244245246247248249250251252253254源代码1.Verilog源代码,dataCollect.vmodule dataCollect(sysclk, rst, adda, addb, addc, start, oe, datain, led_sel, led_seg); input sysclk, rst; input wire [7:0] datain; output reg adda, addb, addc, start, oe; output reg[3:0] led_sel; output reg[7:0] led_seg; reg [3:0] counter1; reg [7:0] readdata; reg [9:0] counter2; reg [15:0] sum; reg [7:0] averdata; reg [7:0] temp; reg [3:0] dataout1, dataout2, dataout3; reg [3:0] counter3; parameter ZERO = 8'b11111100,ONE = 8'b01100000, TWO = 8'b11011010; parameter THREE = 8'b11110010, FOUR =8'b01100110; parameter FIVE = 8'b10110110, SIX = 8'b10111110, SEVEN =8'b11100000; parameter EIGHT = 8'b11111110, NINE = 8'b11110110, BLANK = 8'b00000000; always @(posedge sysclk or negedge rst) begin if (!rst) begin adda = 0; addb = 0; addc = 0; oe = 1; counter1 = 0; end else begin counter1 = counter1 + 1; case (counter1) 3 : start = 0; 4 : start = 1; 5 : start = 0; 10 : readdata = datain; 15 : counter1 = 0; default : counter1 = counter1; endcase end end always @(posedge sysclk or negedge rst) begin if (!rst) begin counter2 = 0; sum = 0; averdata = 0; end else begin counter2 = counter2 + 1; if ((counter2%16) == 0) sum = sum + readdata; else if (counter2 > 512) begin averdata = sum / 32; sum

- Xilinx Kintex UltraScale 一半尺寸的 PCI Express 平台 (HTG-K816)(06-15)

- Xilinx全新参考设计提供业界首个单芯片400G解决方案(02-12)

- Xilinx用于工业自动化的机器视觉解决方案(11-30)

- Xilinx多协议机器视觉摄像机参考设计(12-01)

- 机器视觉技术原理解析及解决方案集锦(02-06)

- 机器视觉在汽车电子方向的应用解决方案(02-13)