7Series FPGA高速收发器使用教程分享

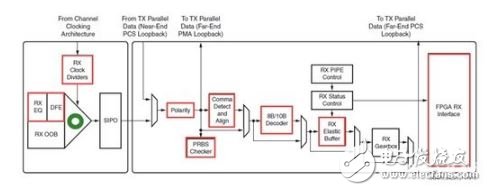

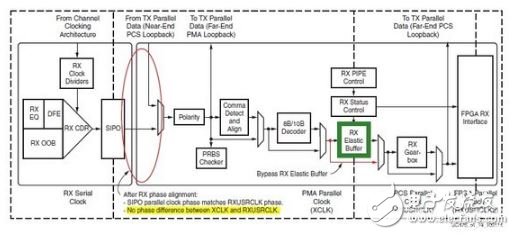

上一篇博文介绍了GTX的发送端,这一篇将介绍GTX的RX接收端,GTX RX接收端的结构和TX发送端类似,数据流方向相反,不过和发送端也有一些区别,GTX的RX接收端结构图如图1所示:

图1

下面将根据数据流方向介绍一下RX接收端各个电路部分的功能。

RX Equalizer (DFE and LPM):RX信号从AFE(模拟前端)进来之后,首先经过RX均衡器,均衡器的主要作用是用于补偿信号在信道传输过程中的高频损失,因为信道是带宽受限的,所以信号经过它必将造成衰减甚至遭到破坏。

RX接收端的均衡器有两种,分别是LPM和DFE,两者功耗和性能有所不同,其中LPM功耗较低,DFE能提供更精确的滤波器参数,从而可以更好的补偿传输信道损失,因此性能更好。

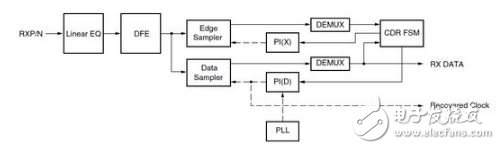

RX CDR:RX的时钟数据恢复电路是图1的绿色圆圈部分,因为GTX传输不带随路时钟,因此在接收端必须自己做时钟恢复和数据恢复,时钟数据恢复电路如图2所示:

图2

具体过程如图2所示,首先外部数据进来之后经过均衡器,紧接着均衡器出来的数据就进入时钟数据恢复电路。GTX使用相位旋转CDR结构,从DFE进来的数据分别被边缘采样器和数据采样器捕获,然后CDR状态机根据两者决定数据流的相位并反馈控制相位内插器(PI),当数据采样器的位置位于眼图中央的时候边缘采样器锁定到数据流的传输域。其中CPLL或者QPLL为相位内插器提供基础时钟,使CDR状态机能很好进行相位控制。

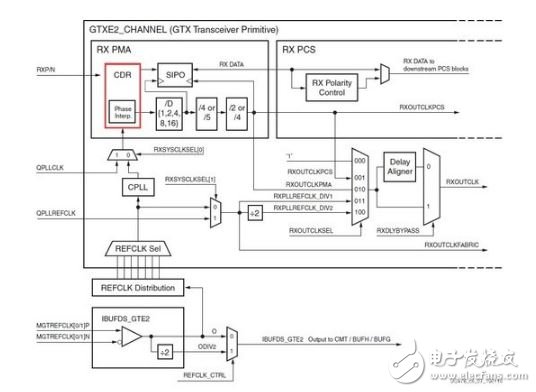

RX Fabric Clock Output Control:RX接收端的时钟结构和TX发送端的很类似,如图3所示,图中红色方框的CDR部分是和TX端最大的区别。

图3

和TX发送端一样,RX接收端的时钟结构也主要分为串行时钟分频器和并行时钟分频器,D分频器是串行时钟分频器,用于降低PLL时钟速率以支持较低的线速率,后面的并时钟分频器主要根据设置的位宽和是否使用8b/10b生成不同的并行数据时钟。

RX Polarity Control:和TX发送端一样,RX接收端也拥有极性控制功能,可用于实现数据翻转,在PCB设计时RXP和RXN接反时使用这个功能。

RX Pattern Checker:GTX包含一个内嵌的PRBS检查器,如图4所示,有四种不同的伪随机序列生成器可以选择,检查器是自同步的,且工作在边界对齐和解码之前,这个功能可以用来测试信号的完整性。

图4

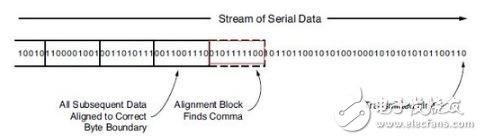

RX Byte and Word Alignment:串行数据在被并行化之前,比如找到一个合适的特征边界,这个特征边界或者字符边界是由TX发送端发送的一个可识别序列,通常称为标识符(comma)或者K码,接收端在到来的数据中搜索这个标识符,当找到这个标识符之后,后面接收的数据都已这个标识符为边界进行并行化,其工作原理如图5所示。

图5

如图5所示,当在串行数据中搜索到comma之后(红色方框),后面的数据都已此为边界对齐数据。

RX 8B/10B Decoder:如果发送端发送的数据是8B/10B编码的,那么在接收端就需要8B/10B解码,否则的话可以旁路,这一功能在TX发送端介绍时有说明,这里就不再做介绍。

RX ElasTIc Buffer:RX接收端弹性缓冲器是一个重要的功能,和TX接收端缓冲相比,RX多出了一个"弹性"属性,意味着和TX发送端相比,RX弹性缓冲器有更多的功能(RX时钟纠正和RX通道绑定)。RX弹性缓冲器在RX接收端的位置如图6绿色方框所示。

图6

从图6可以知道,RX接收端PCS子层主要有两个时钟域,分别是XCLK和RXUSRCLK时钟域,RX弹性缓冲器功能主要用来匹配两个时钟相位差。

如果旁路掉这个RX弹性缓冲器,那么为了保证数据的稳定接收,需要满足一定的条件,首先需要一个相位对齐电路处理SIPO电路时钟和XCLK时钟的相位差,其次XCLK需要配置成RXUSRCLK时钟,保证XCLK和RXUSRCLK同一个时钟域,不存在相位差。

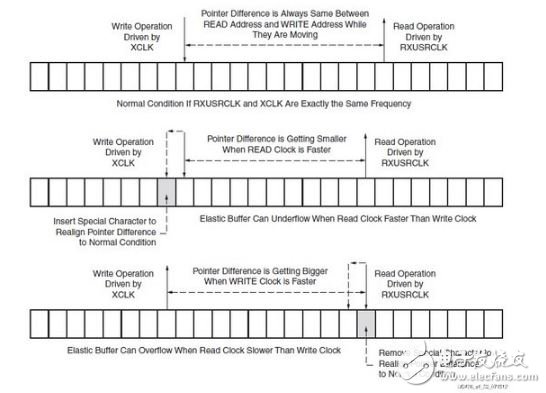

RX Clock CorrecTIon:RX弹性缓冲器的"弹性"反映在可以通过时钟纠正来调整XCLK和RXUSRCLK的频率差。对于RX接收端来说,即便XCLK和RXUSRCLK运行在同一个时钟频率,但往往存在一定的差异,这种差异很容易导致RX弹性缓冲器写满或者读空,时钟纠正功能应运而生。时钟纠正功能如图7所示。

图7

通俗的讲,在TX发送端的时候,我们会定期的发送K码用于保证接收端边界对齐,在RX弹性缓冲器里面数据不足的时候,接收到的K码数据将被复制写入RX弹性缓冲器,以保持RX弹性缓冲器处于半满。当RX弹性缓冲器数据过多的时候,接收到的K码数据将被舍弃不写入RX弹性缓冲器,以保持RX弹性缓冲器处于半满。

RX Channel Bonding:通道绑定功能同样体现RX弹性缓冲器的"弹性"之处,对于像PCIE和SRIO等协议,可以支持多la

- FPGA中的多时钟域设计(02-11)

- 高手DIY,教你将电视改为无线接收(08-05)

- PowerXR EMI降低技术利用扩频时钟抖动(02-19)

- Xilinx Virtex UltraScale 开发平台(06-12)

- 针对汽车应用的本地互连网络LIN收发器NCV7321(10-15)

- 电力线MAC/PHY集成收发器INT51X1及其应用(02-11)