例解电路去耦技术,看了保证不后悔

时间:10-05

来源:

点击:

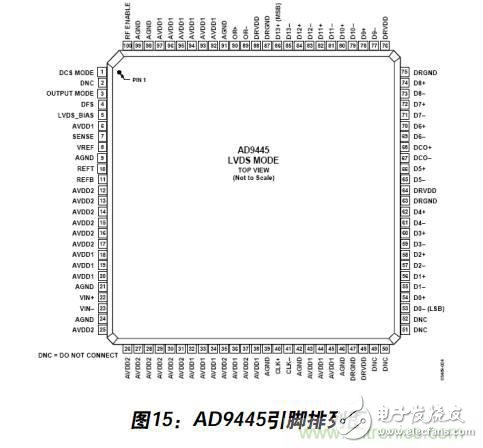

。18个引脚连接到AVDD1(电压为+3.3 V ± 5%),15个引脚连接到AVDD2(电压为+5 V ± 5%)。DVDD(电压为+5 V ± 5%)引脚有4个。在本实验中所用的评估板上,每个引脚具有陶瓷去耦电容。此外还有数个10 F电解电容。

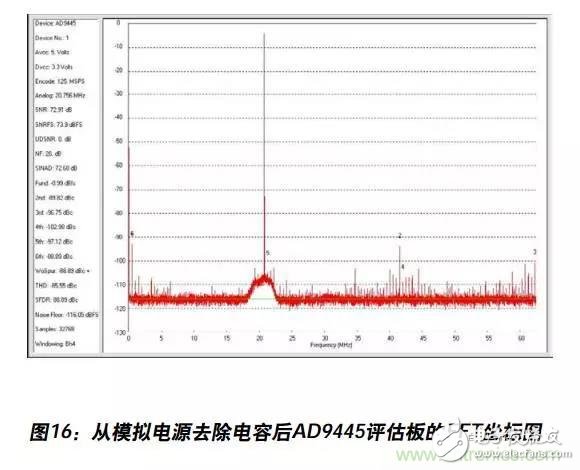

图16显示了从模拟电源去除去耦电容后的频谱。请注意,高频杂散信号增加了,还出现了一些交调产物(低频成分)。

信号SNR已显著降低。

本图与上图的唯一差异是去除了去耦电容。同样使用AD9445评估板进行测量。

图17显示从数字电源去除去耦电容的结果。注意杂散同样增加了。另外应注意杂散的频率分布。这些杂散不仅出现在高频下,而且跨越整个频谱。本实验使用转换器的LVDS版本进行。

可以想象,CMOS版本会更糟糕,因为LVDS的噪声低于饱和CMOS逻辑。

电路去耦 相关文章:

- LT3751如何使高压电容器充电变得简单(08-12)

- 三路输出LED驱动器可驱动共阳极LED串(08-17)

- 浪涌抑制器IC简化了危险环境中电子设备的本质安全势垒设计(08-19)

- 严酷的汽车环境要求高性能电源转换(08-17)

- 适用于工业能源采集的技术 (08-10)

- 单片式电池充电器简化太阳能供电设计(08-20)