例解电路去耦技术,看了保证不后悔

何谓正确去耦?有何必要性?

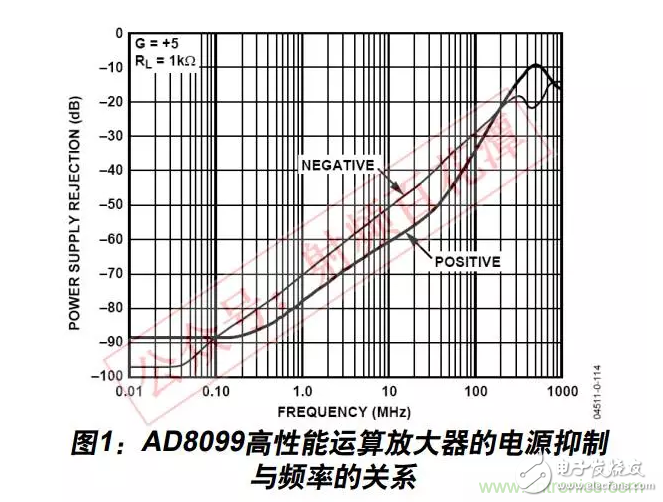

说明模拟IC对电源变化灵敏度的传统参数是电源抑制比(PSRR)。对于放大器,PSRR是输出电压变化与电源电压变化之比,用比率(PSRR)或dB (PSR)表示。PSRR可折合到输出端(RTO)或输入端(RTI)。RTI值等于RTO值除以放大器增益。

图1显示典型高性能放大器(AD8099) PSR随频率、以大约6 dB/8倍频程(20 dB/10倍频程)下降的情况。图中显示了采用正负电源两种情况下的曲线图。尽管PSR在直流下是90 dB,但较高频率下会迅速降低,此时电源线路上有越来越多的无用能量会直接耦合至输出。因此必须一开始就要防止此高频能量进入芯片。一般通过组合电解电容(用于低频去耦)、陶瓷电容(用于高频去耦)来完成,也有可能使用铁氧体磁珠。

数据转换器以及其他模拟和混合信号电路的电源抑制可能在数据手册中都有相关规定。不过,在数据手册的应用部分,经常会针对几乎所有的线性和混合信号IC推荐电源去耦电路。用户应始终遵循这些建议,以确保器件正常工作。

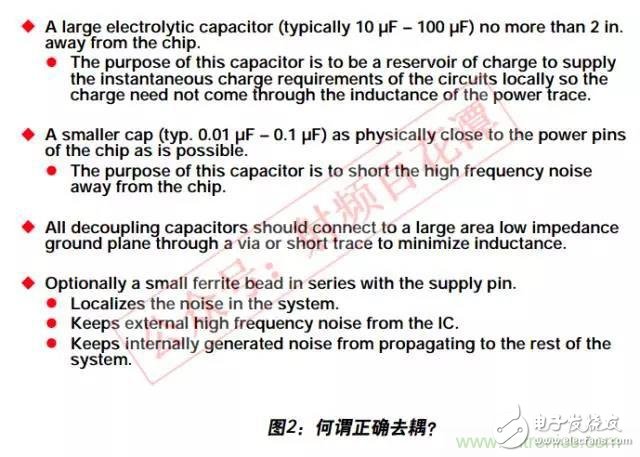

低频噪声需要较大的电解电容,用作瞬态电流的电荷库。将低电感表面贴装陶瓷电容直接连接到IC电源引脚,便可最大程度地抑制高频电源噪声。所有去耦电容必须直接连接到低电感接地层才有效。此连接需要短走线或过孔,以便将额外串联电感降至最低。

铁氧体磁珠(以镍、锌、锰的氧化物或其他化合物制造的绝缘陶瓷)也可用于在电源滤波器中去耦。铁氧体在低频下(<100 kHz)为感性,因此对低通LC滤波器有用。100 kHz以上,铁氧体成阻性(高Q)。铁氧体阻抗与材料、工作频率范围、直流偏置电流、匝数、尺寸、形状和温度成函数关系。

铁氧体磁珠并非始终必要,但可以增强高频噪声隔离和去耦,通常较为有利。这里可能需要验证磁珠永远不会饱和,特别是在运算放大器驱动高输出电流时。当铁氧体饱和时,它就会变为非线性,失去滤波特性。

请注意,某些铁氧体甚至可能在完全饱和前就是非线性。因此,如果需要功率级,以低失真输出工作,当原型在此饱和区域附近工作时,应检查其中的铁氧体。

图2总结了正确去耦的重要方面。

实际电容及其寄生效应

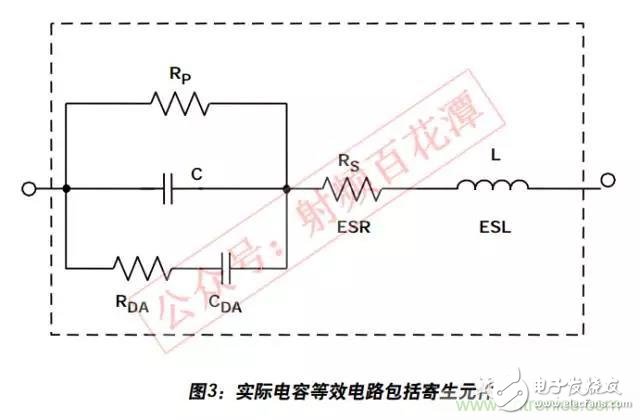

图3显示了一个非理想电容的模型。电阻RP代表绝缘电阻或泄漏,与标称电容C并联。第二个电阻RS(等效串联电阻或ESR)与电容串联,代表电容引脚和电容板的电阻。

电感L(等效串联电感或ESL)代表引脚和电容板的电感。最后,电阻RDA和电容CDA一起构成称为电介质吸收或DA现象的简化模型。在采样保持放大器(SHA)之类精密应用中使用电容时,DA可造成误差。但在去耦应用中,电容的DA一般不重要。

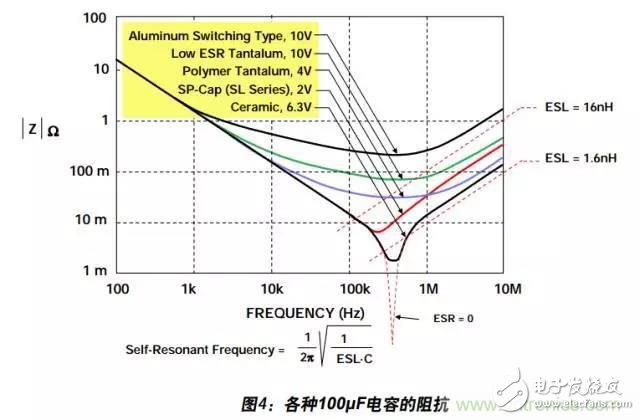

图4显示了各种100 F电容的频率响应。理论上,电容阻抗将随着频率增加呈单调下降。实际操作中,ESR使阻抗曲线变得平坦。随着频率不断升高,阻抗由于电容的ESL而开始上升。"膝部"的位置和宽度将随着电容结构、电介质和等效器件的值而变化。因此常常可以看到较大值电容与较小值电容并联。较小值电容通常具有较低ESL,与较高频率的电容看似相同。这可以在更宽频率范围内扩展并联组合的总体性能。

电容自谐振频率就是电容电抗(1/C)等于ESL电抗(ESL)的频率。对这一谐振频率等式求解得到下式:

所有电容将显示大致形状与图示类似的阻抗曲线。虽然实际曲线图有所不同,但大致形状相同。最小阻抗由ESR决定,高频区域由ESL决定(后者很大程度上受封装样式影响)。

去耦电容类型

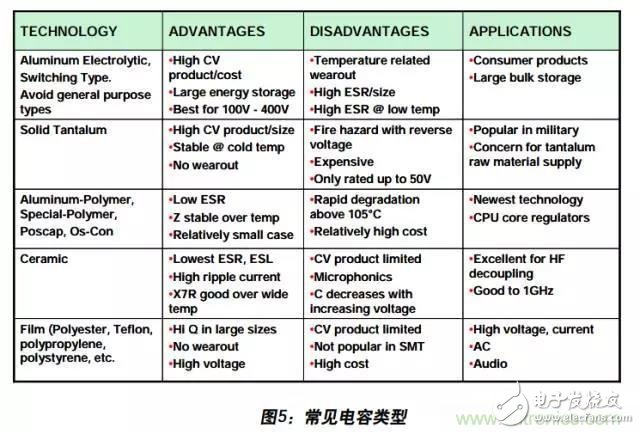

图5显示适合去耦的各种常见电容类型。电解系列具有宽值范围、高电容体积比和广泛的工作电压,是极佳的高性价比低频滤波器元件。它包括通用铝电解开关类型,提供10 V以下直至约500 V的工作电压,尺寸为1 F至数千F(以及成比例的外形尺寸)。

所有电解电容均有极性,因此无法耐受约一伏以上的反向偏置电压而不造成损坏。此类器件具有相对较高的泄漏电流(可能为数十A),很大程度上取决于特定系列的设计、电气尺寸、额定电压及施加电压。不过,泄漏电流不可能是基本去耦应用的主要因素。

大多数去耦应用不建议使用"通用"铝电解电容。不过,铝电解电容的一个子集是"开关型",设计并规定用于在最高达数百kHz的频率下处理高脉冲电流,且仅具有低损耗。此类电容在高频滤波应用中可直接媲美固态钽电容

电路去耦 相关文章:

- LT3751如何使高压电容器充电变得简单(08-12)

- 三路输出LED驱动器可驱动共阳极LED串(08-17)

- 浪涌抑制器IC简化了危险环境中电子设备的本质安全势垒设计(08-19)

- 严酷的汽车环境要求高性能电源转换(08-17)

- 适用于工业能源采集的技术 (08-10)

- 单片式电池充电器简化太阳能供电设计(08-20)