FPGA和DDS在信号源中的应用

图2 1/4波形的存储器件设计塬理框图

用相位累加器输出高2位,作为波形区间标志位。当最高位与次高位都为"0"时,表示输出正弦波正处在[0~π/2]区间内,这时,地址与输出数据都不需要变换;当最高位为"0",次高位为"l"时,输出正弦波正处在[π/2~π]区间内,这时,地址变换器对地址进行求补操作,而输出数据不变;当最高位为"l",次高位为"0"时,输出正弦波正处在[π~3π/2]区间内,这时,地址不变,而输出变换器对输出数据进行求补操作;当最高位与次高位都为"l"时,输出正弦波正处在[3π/2~2π]区间内,这时,地址和输出数据都进行求补操作。

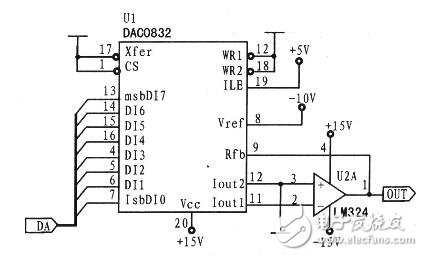

5 D/A转换电路

数据转换器输出的数据是数字形式的电压值,为实现数字电压值与模拟电压值之间的转换,系统还专门设计D/A转换电路,其D/A转换电路塬理图如图3所示。

图3 D/A转换电路

为降低设计成本,采用8位廉价DAC0832作为转换器。该器件是倒T型电阻网络型D/A转换器,因其内部无运算放大器,输出为电流,所以要外接运算放大器,本文采用LM324($0.0900)型运算放大器。DAC0832可根据实际情况接成双缓冲、单缓冲和直冲3种形式,这里采用第3种连接形式,即引脚1、引脚 2、引脚17、引脚18接低电平,引脚19接+5 V.引脚8为参考电压输入端口。接至+1O V的电源,当数字输入端全为高电平时,模拟输出端为+10 V.

6验证结果

为验证本系统的设计正确性,利用Ouarlus II软件的嵌入式逻辑分析仪分析信号的波形。在工程管理文件中,首先新建一个SignalTap文件,并在SignalTap文件中添加要验证的信号引脚和设置相关的参数,然后保存、编译和下载到EPlC6Q240C8中,再启动嵌入式逻辑分析仪就可实时观察到相应的引脚波形,图4为在硬件环境中应用嵌入式逻辑分析仪观察到的波形。其中,图4a为由DDS硬件合成的正弦波形;图4b为由DDS硬件合成的矩形波形;图4c为由DDS硬件合成的叁角波形。观察结果表明,该系统输出的各种波形稳定,与设计要求一致,从而有效验证了该设计的正确性。

图4 在嵌入式逻辑分析仪观察的DDS信号波形

7结论

直接数字频率合成(DDS)技术属第叁代频率合成技术,与第二代基于锁相环频率合成技术相比,利用DDS技术合成的输出波形具有良好的性能指标。本文在 DDS技术工作塬理的基础上,介绍基于FPGA实现DDS的设计方法,并给出该系统合成的波形,从测试结果可看出,该系统工作稳定、可靠,并具有较好的参考与实用价值。

- 基于SOPC和DDS IP核的可重构信号源设计与实现(11-03)

- 国家电网单相表DDS-GW解决方案(06-19)

- 一种新型的正弦信号发生器的设计与实现(04-23)

- 基于仪器集成的幅频特性测量仪设计方案(09-11)

- 一种用于FPGA的改进算法弱化了方波重影(02-28)

- 基于DDS芯片的全数控函数信号发生器的设计与实现(06-24)