不老神话仍在延续:8051必将驰骋IOT时代

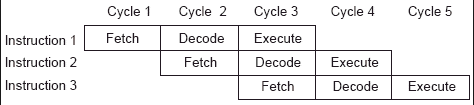

当8051内核架构在1998年失去专利保护后,备受肯定的8051内核再次受到热捧,当时多种新型的8051 MCU不断涌入市场,一些厂家继续采用原始的架构,而另外一些厂家对它进行了不同程度的改进。Silicon Labs 8051架构正是这些更高性能优化架构之一。它保持与原始内核代码兼容,同时对8051架构进行了现代化和"类RISC化",从而获得了巨大的性能提升。图1显示了在Silicon Labs 8051内核中实现的经典三级流水线架构。

图1 - 典型流水线示例

原始的Intel 8051内核执行一条指令需要花费12个时钟周期;因此,在12MHz时钟频率下,它的运行速率可达1MIPS(每秒百万指令)。相比之下,100MHz时钟频率的Silicon Labs 8051内核可达到100MIPS,或者可以说是——在大约8倍于传统8051的时钟频率下,100MHz时钟频率的Silicon Labs 8051内核比传统8051内核运行速率快了100倍。

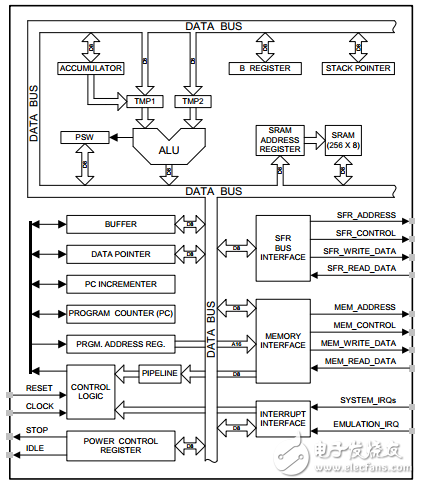

Silicon Labs以3级流水线冯·诺依曼(Von-Neuman)架构来实现它的8051先进内核。3级流水线整合8位机明确的指令解码逻辑的简易性使得这个芯片能够在0.35微米工艺下运行在100MHz时钟频率。由于与经典的8051代码兼容至关重要,该架构保留一个带有4个区域的32字节的寄存器文件,从而能够更容易的进行上下文切换。经典8051的所有其他硬件方面也由于上面提及的原因而得到保留。图2显示了新一代Silicon Labs芯片中实现的8051内核。

图2 - 最先进技术的8051 MCU示例

为了充分利用这些新型8051芯片的功能,需要创建一个系统定义识别并利用这种架构所提供特性的系统定义。例如,8051内核实现了可在某些寄存器或存储位置直接执行逻辑运算操作的能力。这在几乎任何控制应用中都是一项非常有用的特性,无论是工业还是其他领域。凭借Silicon Labs 8位芯片的运行频率,这些操作能够在单个时钟周期内完成执行。这种方法带来极佳的控制响应时间,这意味着当与相同配置的硬件实现相比时,bit-banged的总线定义能够以一种相当合理的速率运行。例如,bit-banged的全双工SPI能够被实现为每位12个系统时钟周期,在100MHz系统时钟频率下支持大于8MHz的位传输频率。

另一项8051创新是为带有嵌入闪存的闪存存储器管理增加控制器,这为8051带来快速启动和执行代码的能力。当然,指令取出路径也要满足速度需求,因此诸如预取指缓冲器、缓存和分支目标缓冲器这些高级特性也要被实现。Silicon Labs最新的8位MCU,例如EFM8UBx系列产品,实现了传统的16位宽预取指缓冲器以支持50MHz操作。

鉴于这些系统的性能特点,新颖的I/O架构必须支持多种外设才能够同时(或者分时共享)运行。为此目的,开发一个基于优先级的Crossbar架构才能允许任意外设以确定的方式,访问几乎任意端口。因此,在带有大量I/O引脚的相同系统中实现多种高速外设成为可能,并且所有引脚都可以通过高性能CPU控制。

8051内核是8位机器,这意味着寄存器空间被限制仅仅能支持256个寄存器。仅具有高性能CPU和众多外设,这是远远不够的。为了克服寄存器空间的限制,存储页的概念被用于实现多个256字节地址空间定义,并且页切换的机制也被实现。此外,某些系统寄存器以及关键外设寄存器在每一个页中都是可访问的。

----------------------------------------------------------

本文选自4月份《智能硬件特刊》,更多技术热文可进入特刊详情页面下载浏览!

原始8051内核的另一个缺点是它的中断延迟。由于它固有的12时钟周期执行延迟,中断延迟可能需要数百个时钟周期,这使得它仅适用于慢速控制。更高性能的芯片显而易见有更短的中断延迟,因此缩短了对控制/传感器中断的整体系统响应时间。有些新晋的Silicon Labs 8051 MCU也在他们的中断级中实现了4个中断优先级状态。这种技术使得中断处理更加精确,这在一个拥有大量外设的系统中是必须的。

就新近系统存储器的固有特性而言,实际上存储访问需要占用2个时钟周期。因此,每一次存储器访问之后能够跟随任意其他动作,并且不会导致流水线溢出。在存储器位置上执行逻辑操作的能力也得到保留,它们也作为2个时钟周期操作,因为它们采用"读取-修改-写回"的操作方式。

尽管有相对高的时钟速率,但是高性能8051 MCU并非为执行高速高阶算法而设计。例如,16位的乘法在Silicon Labs 8051 MCU上将需要占用143个时钟周期。Silicon Labs的一些高速8051 MCU也实现了一个带有40位累加器的16位MAC。这种技术完成了单时钟周期的16位MAC操作或者乘法运算。当然,它仍然需要几个时

- 如何做一个高集成低能耗的BMS系统(02-23)

- Thread/ZigBee网状网络模块助力IoT平台(09-17)

- 回顾世强& Silicon Labs “2017 Wireless Workshop”,了解最新物联网技术(09-18)

- 51单片机+CPLD让系统更高效(10-25)

- 电子电路设计之C51单片机常见问题(10-22)

- C51单片机看门狗电路(02-14)