八核浮点型DSP的双千兆网接口设计方案

的接口

MDIO和MDCLK 为TMS320C6678内部MDIO 模块的数据和时钟,用于TMS320C6678和88E1111建立连接,TMS320C6678可以通过该接口配置88E1111,或者读取88E1111的信息。由于88E1111的MDIO模块接口电平为2.5V,而TMS320C6678的MDIO模块接口电平采用1.8V电压,所以两者之间需要增加电压转换芯片,本设计采用PCA9306实现电压转换,接口电路如图5所示。

图5 MDIO接口的电压转换电路

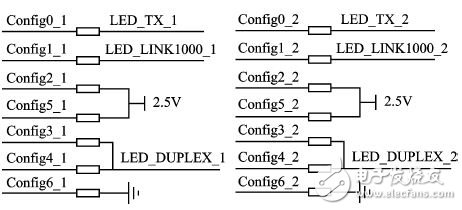

需要注意的是,由于存在两个88E111芯片,MDIO和MDCLK引脚直接连接到两个芯片上,MDIO可以最多控制32个物理层芯片,物理层芯片地址分别为1~32.88E1111的地址配置如图6所示。

图6 88E1111的硬件配置

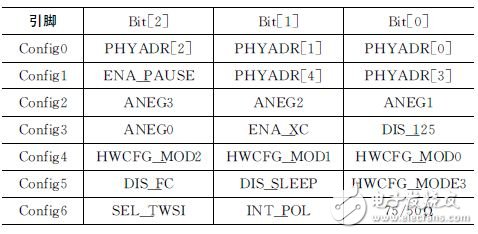

表1为对应的配置信息,根据图6和表1,可以看出88E111的地址分别为4和8。

表1 配置引脚设置

4. 软件设计

系统软件设计包括硬件初始化、网络配置以及数据通信流程等。TMS320C6678复位后的工作流程如图7所示。首先配置第一个网口,记录其状态后配置第二个网口。只要两个网口有一个配置成功,将配置TMS320C6678的EMAC模块,为成功配置的网口设置收发缓冲和收发任务。这些配置好后,就可以实现网络的数据收发。需要注意的是,在用户应用程序中,需要考虑到网口配置失败的情况。例如,用户应用程序通过双网口实时传输1.2Gbps的数据,如果一个网口配置失败,则应用程序应有相应的机制将实时传输速率降低到0.8Gbps以下(单网口实际传输速率可能低于0.8Gbps)。本文硬件系统在没有其他任务开销情况下,实测可以传输1.5Gbps的数据(传输过程中不考虑错误,不进行重发)。

图7 数据通信流程

结语

超过1Gbps传输速率的通信接口一般采用光纤、PCE、PCIe等接口方式。本文采用双网口方式可以降低设备要求,和既有设备方便连接。使用多核DSP提高处理器工作能力,在保证大容量数据传输过程中,处理器仍然具有对数据的计算能力。双网口设计方案可以弥补单网口的传输速率不足,又可以降低其他接口的硬件复杂度,是介于两者之间的有益补充。在嵌入式设备中具有一定的应用价值。

- 基于TMS320C6678的多核DSP上电加载技术(02-26)

- Telematics的应用模式与系统设计要领(06-22)

- 西门子SIMATIC系统在安全防爆方面的应用(08-28)

- 低照性能的突破——照亮IP视频摄像机应用前景(11-12)

- TI家用能源显示设备方案(03-12)

- 飞兆、NXP、TI、安森美四家LED驱动方案大比拼(04-07)