八核浮点型DSP的双千兆网接口设计方案

千兆网络接口具有数据传输速率快、连接方便、可以即插即用的优点,使得其应用较为广泛。随着电子技术和处理器的发展,很多应用场合的数据通信速率超过千兆网口的实际传输速率。例如,在A/D采样中,需要直接存储A/D转换的采样数据,如果A/D转换位数为16位,工作在100MHz,则实际数据量为1.6Gbps。为了实现高速传输,必须采用更高传输速率的接口,例如PCIe或者RapidIO接口。但这些接口不具有即插即用功能,与很多工业既有设备不能直接连接,限制了其应用场合。

DSP(数字信号处理器)具有较高的工作频率,其内部集成硬件网络MAC接口,外接一个物理层芯片就可以方便地实现千兆网络通信。多核DSP芯片可以连接多个千兆网口,使得其可以应用到高速数据传输场合。本文介绍一种基于多核数字信号处理器TMS320C6678的嵌入式双千兆网络接口,实现单个芯片连接两个千兆网口,这两个网口可以各自独立传输数据,也可以联合传输数据,提高了实际的数据传输速率。

1. C6678及其结构

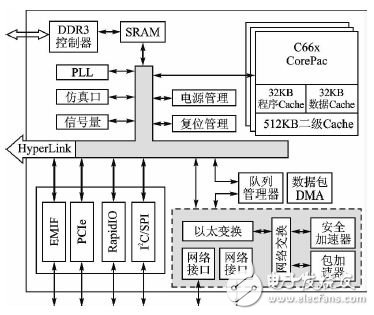

TMS320C6678是TI公司多核处理器中的一款8核浮点型DSP,每个核最高工作频率可达1.25GHz,每个核可以提供40GMAC定点计算或者20GFLOP浮点计算能力,单个芯片可以提供320GMAC或者160GFLOP计算能力。TMS320C6678的片内结构如图1所示。

TMS320C6678的每个核具有32KB的程序、32KB的数据以及512KB的2级Cache存储空间,芯片片内具有一个4MB的共享SRAM。TMS320C6678具有DDR3控制器接口,可以外接DDR3,直接寻址范围达到8GB。TMS320C6678的片内外设有RapidIO、PCIe、EMIF、SPI、I2 C总线等接口。这些接口通过片内的高速互联总线和各个处理器交互数据。

和网络相关的片内设备如图1右下角灰色模块所示,主要包括两个对外的SGMII接口、以太交换和网络交换模块,以及用于数据管理的安全加速器和包加速器,可以快速检测数据的校验以及协议是否遵循网络标准,对于错误的数据直接丢弃,降低CPU 的负担。为了加快网络和CPU的数据交换,片内的队列管理器用于管理网络包或者网络帧的缓存、分发等功能。这些数据都采用数据包DMA读写,不需要CPU参与。

图1 TMS320C6678内部结构图

TMS320C6678的其他片内设备包括PLL、仿真口、信号量、电源管理和复位管理等模块。其中PLL配置CPU和外设的工作时钟;仿真口用于连接仿真器,实现对软件运行的监控;信号量实现对DSP/BIOS操作系统中信号量的控制;电源管理实现整个芯片电流电压的控制;复位管理配置启动的方式,硬复位进行全启动,软复位进行部分启动。

2. 88E1111及其结构

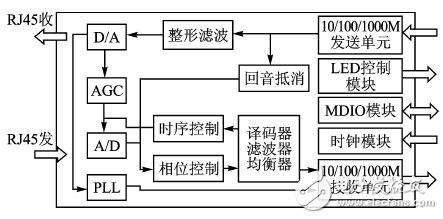

网络物理层芯片很多,一般都兼容MII、RMII以及SGMII等接口标准之一或者多个。但TMS320C6678只提供了SGMII接口,所以和TMS320C6678连接的物理层芯片必须具有SGMII接口。本文使用两片Marvell公司的88E1111 物理层芯片进行双千兆网络的连接。88E1111的片内结构如图2所示。

图2 88E1111内部结构图

网络RJ45接口发送过来的带有调制数据的模拟信号经过A/D转换变成数字信号,然后依次经过均衡、整形滤波和译码后由接收单元传输到MAC芯片,实现数据的接收。MAC发送的数据经过整形滤波后由D/A转换成模拟信号发送到RJ45接口。为了降低误码率,88E1111内部具有锁相环(PLL)、自动增益控制(AGC)、时序/相位控制、回音抵消等模块,这些模块都是为了提高数据传输的可靠性,在不同环境或者不同外接设备下,都可以高速可靠地通信。图2中的LED控制模块实现数据传输时的灯光显示,MDIO模块实现链接建立和状态监测,时钟模块提供工作时钟。

3. 硬件设计

硬件设计主要包括TMS320C6678和两个88E1111的接口、88E1111和RJ45的接口、88E1111的硬件配置设计等几个部分。

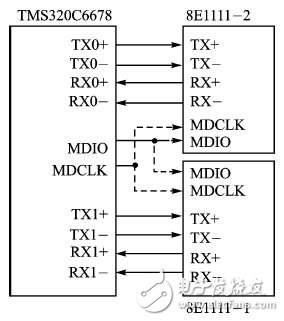

TMS320C6678的网络模块结构如图3所示。片内集成了一个3口的以太交换机,负责将两个千兆网口的数据交换到主机,同时提供交换中断到主机,主机通过中断可以实时接收和发送数据。主机通过总线配置或者监控外部的物理层芯片,配置和监控数据通过MDIO接口连接到物理层芯片。

图3 TMS320C6678网络模块结构

图4 TMS320C6678和88E1111的接口TMS320C6678和两片88E1111的接口电路如图4所示。TMS320C6678 采用SGMII(Serial Gigabit Media Independent Interface)接口,兼容10/100/1000M 工作方式。SGMII为串行数据收发方式,具有较少的引脚连接。从图4中可以看出,实际上只有两对收发的差分线,分别连接到对应的88E1111引脚上。读写时钟隐含在数据上传输,由硬件自动识别,无须软件参与。

图4 TMS320C6678和88E1111

- 基于TMS320C6678的多核DSP上电加载技术(02-26)

- Telematics的应用模式与系统设计要领(06-22)

- 西门子SIMATIC系统在安全防爆方面的应用(08-28)

- 低照性能的突破——照亮IP视频摄像机应用前景(11-12)

- TI家用能源显示设备方案(03-12)

- 飞兆、NXP、TI、安森美四家LED驱动方案大比拼(04-07)