GPIB控制器软件的IP核设计方案详解

随着网络技术与通信技术的高速发展,测试仪器和测试技术发生了革命性变化,"网络就是仪器"确切地概括了测试仪器间的网络化发展趋势。组建网络化测试系统不仅能实现资源共享,而且组建系统方便,还可提高测试系统的复杂度,拓宽其应用范围。笔者采用CPLD 芯片实现GPIB 控制器的IP 核设计完成芯片NAT 9914 的产权自主化,从而大大降低了开发成本。

1 GPIB 控制器方案设计

通用接口总线( General Purpose Interface Bus,GPIB) 使自动化测试仪器的互联有了统一的标准,极大地推动了自动测试技术的发展。GPIB 总线具有并行总线传送速度快、有效数据速率高、驱动能力强、通信距离可达20m、抗干扰能力良好及通用性特点,总线上最多可挂接15 台设备并且传输速度可以达到8Mbit /s,因此有良好的应用前景[1],其自动测试系统组建如图1 所示。

图1 GPIB 控制器组建的自动测试系统框图

GPIB 控制器IP 核设计采用模块化思想,主要模块包括状态机模块、数据通路模块和译码电路模块。对状态机模块的设计包括8 个小模块( 如源方挂钩及受方挂钩等) ,采用VHDL 语言对各个小模块进行编程实现,最后调用各子模块并用原理图的方式进行状态机顶层模块设计,并在Synplify 以及QuartusⅡ平台进行分析和仿真。对数据通路的设计也采用同样的方式,先对各个子模块进行设计,然后进行整体设计。最后调用状态机顶层模块、数据通路顶层模块及多线消息译码电路模块等进行GPIB 控制器IP 核的顶层设计。完成整个IPCore设计后,通过JTAG 下载方式将Core 下载到选定的DE2 专用开发套件CPLD 芯片进行通信设置验证,成功后再搭建硬件,从而得到实体化GPIB 控制器。

2 GPIB 控制器IP 核设计的实现

2. 1 接口控制电路的工作原理

GPIB 总线是一种24 芯的并行无源总线,由8根地线和16 根信号线组成。16 根信号线为8 根数据线( DIO1 ~ DIO8) 、3 根握手线( DAV、NRFD、NDAC) 和5 根管理线( ATN、REN、IFC、EOI、SRQ) 。数据传输采用位并行、字节串行的双向异步传输方式。需要注意的是: GPIB 采用的是负逻辑,即低电平( 不大于0. 8V) 为逻辑1,高电平( 不小于2. 0V)为逻辑0[2]。

GPIB 总线的基本原理是将控者作为服务器,利用编程并通过GPIB 总线实现对各个仪器的控制,同时各个仪器也通过操作GPIB 控制芯片来实现与服务器的数据传输,其输出到GPIB 母线上的信号符合IEEE488 标准,从而达到自动控制和测试的目的。

2. 2 模块设计

GPIB 控制器的设计主要包括3 个模块: 接口功能模块、多线消息译码器和数据通路模块。

2. 2. 1 与GPIB 母线通信的接口功能模块

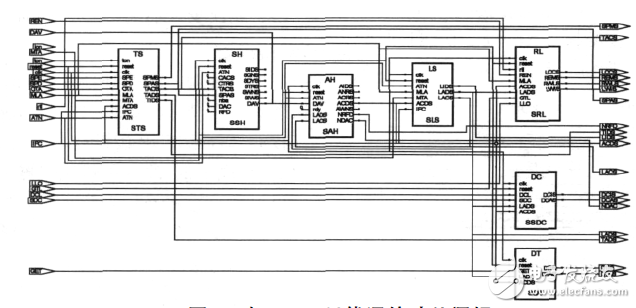

在GPIB 系统中,把器件与GPIB 总线的一种交互作用定义成一种接口功能,实质上是一组逻辑功能,实现IEEE488 通信协议。该功能模块是本设计的重点,在接口功能子集的选择上也有一定的要求,主要实现各子接口功能,即: 源方挂钩SH、讲者T、听者L、服务请求SRQ 及远控本控RL 等。各接口模块功能采用同步MOORE 状态机( 只与当前信号有关,与输入信号无关) 实现。在各子接口模块功能实现的基础上,对其进行顶层状态机设计,即:调用各子模块,用原理图方式对其进行互联式设计,并用VHDL 语言完成对状态机的描述,实现的逻辑功能如图2 所示。其中,输入信号有: GPIB 母线信号( ATN、DAV、IFC、REN、NDAC、NRFD、EOI、SRQ) ,多线消息( MTA、MLA、OTA、LLO、GTL、GET、DCL、SDC、UNL、SPD、SPE) ,辅助寄存器产生的内部消息及本地消息( swrst、lon、rsv、ton) 等。这些输入的信号均通过译码电路产生,输出信号对接口功能的状态进行控制。

图2 与GPIB 母线通信功能逻辑

下面以源方挂钩SH 为例说明其逻辑的实现,逻辑图如图3 所示。

图3 SH 功能实现的逻辑电路

主要代码为:

IF RESET = ‘1’OR( NOT ATN AND NOT( LACS

OR LADS) ) = ‘1’THEN C_ST < = ST1; RFD <

= ‘1’; DAC < = ‘1’;

AIDS < = ‘ 1’; ANRS < = ‘ 0’; ACRS < = ‘ 0’;

AWNS < = ‘0’; ACDS < = ‘0’;

ELSIF CLK‘EVENT AND CLK = ’0‘ THEN

CASE C_ST IS

WHEN ST1 = > IF ATN = ’1‘OR LACS = ’1‘OR

LADS = ’1‘THEN C_ST < = ST2; RFD < = ’0‘;

DAC < = ’0‘; AIDS < =

- 一种消防应急灯具专用控制芯片的设计(11-02)

- 基于FPGA的8段数码管动态显示IP核设计(02-03)

- 基于FPGA和IP Core的定制缓冲管理的实现(08-14)

- 基于Altera ASI IP核的ASI发送卡实现(02-25)

- FPGA的高速多通道数据采集控制器IP核设计(04-22)

- 基于EDA或FPGA的IP保护的实现(09-16)