CMOS图像传感器的基本原理及设计考虑

二极管型结构、针型光电二极管(PPD)结构和光栅型有源像素结构等。

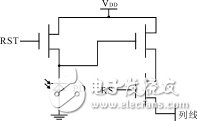

5.1CMOS PPS像素结构设计

光电二极管型CMOS无源像素传感器(CMOS PPS)的结构自从1967年Weckler首次提出以来实质上一直没有变化,其结构如图1所示。它由一个反向偏置的光敏二极管和一个开关管构成。当开关管开启时,光敏二极管与垂直的列线连通。位于列线末端的电荷积分放大器读出电路保持列线电压为一常数,并减小KTC噪声。当光敏二极管存贮的信号电荷被读出时,其电压被复位到列线电压水平,与此同时,与光信号成正比的电荷由电荷积分放大器转换为电荷输出。

单管的PD CMOS PPS允许在给定的像素尺寸下有最高的设计填充系数,或者在给定的设计填充系数下,可以设计出最小的像素尺寸。另外一个开关管也可以采用,以实现二维的X Y寻址。由于填充系数高且没有许多CCD中多晶硅叠层,CMOS PPS像素结构的量子效率较高。但是,由于传输线电容较大,CMOS PPS读出噪声较高,典型值为250个均方根电子,这是致命的弱点。

5.2 CMOS APS的像素结构设计

几乎在CMOS PPS像素结构发明的同时,科学家很快认识到在像素内引入缓冲器或放大器可以改善像素的性能。虽然CMOS图像传感器的成像装置将光子转换为电子的方法与CCD相同,但它不是时钟驱动,而是由晶体三极管作为电荷感应放大器。在一些CMOS图像传感器中,每组像素的顶端有一个放大器,每个像素只有一个作为阈值电流值开关的三极管。开关像素中的电荷为放大器充电,其过程类似DRAM中的读取电路,这种传感器被称为PPS。PPS的结构很简单,它具有高填充系数。各像元没有很多的多晶硅层覆盖,其量子效率很高,但是PPS的读取干扰很高,只适应于小阵列传感器。

在CMOS APS中每一像素内都有自己的放大器。CMOS APS的填充系数比CMOS PPS的小,集成在表面的放大晶体管减少了像素元件的有效表面积,降低了"封装密度",使40%~50%的入射光被反射。这种传感器的另一个问题是,如何使传感器的多通道放大器之间有较好的匹配,这可以通过降低残余水平的固定图形噪声较好地实现。由于CMOS APS像素内的每个放大器仅在此读出期间被激发,所以CMOS APS的功耗比CCD图像传感器的还小。与CMOS PPS相比,CMOS-APS的填充系数较小,其设计填充系数典型值为20%~30%,接近内线转换CCD的值。

5.2.1 光敏二极管CMOS APS(PD CMOS APS)的像素结构

1968年,Noble描述了PD CMOS APS。后来,这种像素结构有所改进。PD CMOS APS的像素结构如图2所示。

高性能CMOS APS由美国哥伦比亚大学电子工程系和喷气推进实验室(JPL)在1994年首次研制成功,像素数为128×128,像素尺寸为40μm×40μm,管芯尺寸为6.8mm×6.8mm,采用1.2μmCMOSn阱工艺试制,动态范围为72dB,固定图形噪声小于0.15%饱和信号水平。固定图形噪声小于0.15%饱和信号水平。1997年***东芝公司研制成功了640×480像素光敏二极管型CMOS APS,其像素尺寸为 5.6μm×5.6μm,具有彩色滤色膜和微透镜阵列。2000年美国Foveon公司与美国国家半导体公司采用0.18μmCMOS工艺研制成功 4096×4096像素CMOS APS[10],像素尺寸为5μm×5μm,管芯尺寸为22mm×22mm,这是迄今为止世界上集成度最高、分辨率最高的CMOS固体摄像器件。有关CMOS APS的工作原理、发展现状及其应用,笔者已作过详细介绍[6]~[8]。

因为光敏面没有多晶硅叠层,PD CMOS APS的量子效率较高,它的读出噪声由复位噪声限制,典型值为75均方根电子~100均方根电子。PD CMOS APS的每个像素采用3个晶体管,典型的像元间距为15μm。PD CMOS APS适宜于大多数低性能应用。

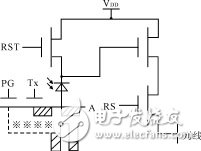

5.2.2 光栅型CMOS APS(PG CMOS APS)的像素结构

1993年由JPL最早研制成功PG CMOS APS并用于高性能科学成像的低光照明成像。PG CMOS APS结合了CCD和X Y寻址的优点,其结构如图3所示。

光栅信号电荷积分在光栅(PG)下,浮置扩散点(A)复位(电压为VDD),然后改变光栅脉冲,收集在光栅下的信号电荷转移到扩散点,复位电压水平与信号电压水平之差就是传感器的输出信号。

当采用双层多晶硅工艺时,PG与转移栅(TX)之间要恰当交叠。在光栅与转移栅之间插入扩散桥,可以采用单层多晶硅工艺,这种扩散桥要引起大约100个电子的拖影。

光栅型CMOS APS每个像素采用5个晶体管,典型的像素间距为20μm(最小特征尺寸)。采用0.25μmCMOS工艺将允许达到5μm的像素间距。浮置扩散电容的典型

- CMOS和CCD传感器的分类和特点详解(02-12)

- 思比科系列CMOS图像传感器应用方案(06-16)

- 透过 iPhone7 Plus双摄像头“窥”CMOS的市场(09-12)

- X京元电、胜丽后市销售看涨的原因——车用CMOS图像传感器需求增加(08-27)

- LT3751如何使高压电容器充电变得简单(08-12)