DSP in FPGA:FIR滤波器(一)

FIR 滤波器广泛应用于数字信号处理中,主要功能就是将不感兴趣的信号滤除,留下有用信号。FIR滤波器是全零点结构,系统永远稳定;并且具有线性相位的特征,在有效频率范围内所有信号相位上不失真。在无线通信收发机中的DDC/DUC模块,抽取和内插都需要加入滤波器以防止信号在频谱上混叠,最典型的是采用 FIR滤波器实现半带滤波器。

FIR滤波处理如下式所示,其中x(n)为输入信号,h(n)为FIR滤波系数,y(n)为经过滤波后的信号;N表示FIR滤波器的抽头数,滤波器阶数为N-1。

由上式可得到FIR滤波器在FPGA中的实现结构,如图1所示,主要由延迟单元Z-1、乘法器和累加器组成。此结构为直接型FIR滤波器结构,也称横向结构(transverse)。

图1

设计FIR滤波器的方法有多种,其中Matlab软件提供了很多关于滤波器设计的工具箱,FDATool就是一个很好的工具,如图2所示就是FDATool的界面,可以在Matlab的Command窗口中直接输入FDATool命令来调用。

图2

滤波器的设计首先需要设置的参数:

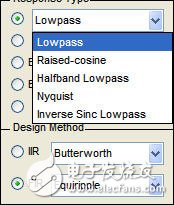

(1) Response Type:选择FIR滤波器的类型:低通、高通、带通和带阻等。如图3所示为Lowpass中的下拉选项,在DDC/DUC模块设计中,抽取和内插需要使用Halfband Lowpass类型,而channel filter需要使用Raised-cosine类型。

图3

(2) Design Method:FIR滤波器设计方法有多种,如图4所示,最常用的是窗函数设计法(Window)、等波纹设计法(Equiripple)和最小二乘法 (Least-Squares)等。其中窗函数设计法在学校课堂中是重点讲解的,提到FIR滤波器肯定会想到hamming、kaiser窗,但是实际应用中却很少使用,因为如果采用窗函数设计法,达到所期望的频率响应,与其它方法相比往往阶数会更多;而且窗函数设计法一般只参照通频带wp、抑制频带ws 和理想增益来设计滤波器,但是实际应用中通频带和抑制带的波纹也是需要考虑的,那在这种情况下,采用等波纹设计法就非常适用了。

图4

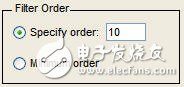

(3) Filter Order:设置滤波器的阶数,这个选项直接影响滤波器的性能,阶数越高,性能越好,但是相应在FPGA实现耗用的资源需要增多。在这个设置中提供2个选项:Specify order和Minimum order,Specify order是工程师自己确定滤波器的阶数,Minimum order是让工具自动确定达到期望的频率相应所需要的最小阶数,因此具体选择哪个选项得视实际情况而定了。

图5

(4) Frequency Specification:设置频率响应的参数,包括采样频率Fs、通带频率Fpass和阻带频率Fstop。

图6

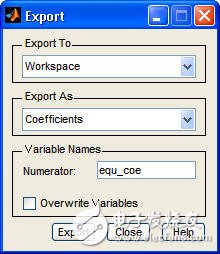

参数设置完成后,FDATool就会分析并且生成滤波系数,如图7所示,可以得到滤波器的频率相应曲线,并且可以通过File-》Export导出滤波系数,如图8所示。

图7

图8

为了快速验证FIR滤波器的FPGA实现,使用Xilinx的System Generator工具,如图9所示为FIR滤波器的验证模型,其中通过Gateway In和Gateway out模块分隔matlab simulink模块和Xilinx FPGA模块,matlab simulink模块用于产生测试源,接收并显示滤波后波形。还有System Generator Token用于生成Xilinx FPGA模块的HDL代码。

图9

其中FIR Compiler 5.0模块的参数设置如图10所示,滤波系数直接调用FDATool生成的滤波系数equ_coe,输出为全精度数据。

图10

得到输出结果如图11所示,上边图为输入原波形,由两个频率分量的正弦波叠加而成,频率分别为2MHz和100MHz,经过FIR滤波之后,100MHz频率分量被滤除。

图11

FIR滤波器根据输入数据速率的不同可分为串行结构、半并行结构和全并行结构。串行结构的FIR滤波器是将并行数据串行输入,所需的DSP资源较少,但是数据吞吐率较低;而全并行结构的FIR滤波器数据是并行输入,滤波系数的个数就决定了所需DSP资源的个数,资源耗用较多,但是吞吐率可以做到很大。在大多数应用中,如无线数字中频处理,所需数据吞吐率一般都较高,因此采用的是全并行结构的FIR滤波器。

全并行FIR滤波器根据实现结构不同可分为:直接型(Transverse)、转置型(Transpose)和脉动型(Systolic),这一节主要讲解直接型FIR滤波器设计。

(一)直接型

直接型FIR滤波器在上一节中也有介绍,如图1所示,数据x(n)移入并寄存,如果有11个抽头,因此直接型FIR滤波器需要11个乘加模块。

图1

FPGA实现时,直接采用上图中结构,不对中间数据寄存,则关键路径是x(n)h(0)+x(n-1)h(1)…x(n-N+1)h(N-1),以阶数10的FIR滤波器为例,如下为抽头系数:

- 智能电网的核心--GreenFire系统(02-12)

- 人工智能处理器三强Intel/NVIDIA/AMD谁称霸?(07-23)

- 基于FPGA和IP核的FIR低通滤波器的设计与实现(11-03)

- 三种完整的硬件Fire Wall解决方案(10-04)

- DSP in FPGA:FIR滤波器(二)(05-30)

- 使用FPGA构建的数字滤波器设计方案(06-24)